# PERFORMANCE AND RELIABILITY ENHANCEMENT TECHNIQUES FOR TWO DIMENSIONAL NETWORK-ON-CHIPS USING ADAPTIVE DEFLECTION ROUTERS

#### Submitted to

## COCHIN UNIVERSITY OF SCIENCE AND TECHNOLOGY

for the award of the degree of

**Doctor of Philosophy**

By

SIMI ZERINE SLEEBA

Under the guidance of

PROF. (DR.) MINI M.G.

RESEARCH GUIDE

DEPARTMENT OF ELECTRONICS ENGINEERING

MODEL ENGINEERING COLLEGE

COCHIN, INDIA -682021

DECEMBER, 2017

## Performance and Reliability Enhancement Techniques for Two Dimensional Network-on-Chips using Adaptive Deflection Routers

#### Ph.D. Thesis

#### **Author:**

Simi Zerine Sleeba Research Scholar Department of Electronics Model Engineering College Thrikkakara, Kochi simi.abie@gmail.com

## **Supervising Guide:**

Dr. Mini M.G.

Professor in charge of Principal

College of Engineering, Cherthala, India

&

Research Guide,

Department of Electronics Engineering

Model Engineering College, Cochin, India - 682021

mininair@mec.ac.in

December, 2017

To

My beloved parents

&

My loving husband and children

## **DECLARATION**

I hereby declare that the work presented in this thesis entitled "Performance and Reliability Enhancement Techniques for Two Dimensional Network-on-Chips using Adaptive Deflection Routers" is a bonafide work carried out by me, in the Department of Electronics Engineering, Model Engineering College, Kochi under the supervision of Dr. Mini M.G., Professor in charge of Principal, College of Engineering, Cherthala and Research Guide, Model Engineering College, Kochi. The results presented in this thesis or part of it have not been presented for the award of any other degree(s).

Kochi, Simi Zerine Sleeba

04-12-2017

## **ACKNOWLEDGEMENTS**

I thank God Almighty for his abundant grace that gave me some wonderful years of research life and experience at Model Engineering College since December, 2011. I would like to express my appreciation to many people who have positively influenced my journey in many ways.

I fall short of words when it comes to expressing my gratitude to Prof.(Dr.) Mini M.G., my research supervisor for her excellent guidance and continuous support throughout these years. With her inspiring words and unbeatable courage in times of distress, I am extremely blessed to have her as my supervisor.

I express my sincere thankfulness to Prof.(Dr.) V.P. Devasia, Principal, Model Engineering College for his valuable comments and providing all research facilities during my tenure in the institution.

It is a great privilege that I could associate with Prof. (Dr.) John Jose, Assistant Professor, Department of Computer Science and Engineering, IIT Guwahati who is a passionate teacher and researcher. I am filled with extreme gratitude for the selfless help extended by him through enormous hours spent in manuscript corrections and discussions.

I would like to thank Prof. (Dr.) Jayasree V.K., Former Head of Department of Electronics, Model Engineering College for her valuable help. Special thanks to Shri. Jagadeesh Kumar P., Associate Professor in the Department of Electronics for providing me with lab facilities during the initial years. Working with my friends and co-researchers at Model Engineering

College, especially Shri. Anoop T.R., Mrs. Asha R.S. and Mrs. Neethu M. Sasi, has been the most memorable part of these years. Furthermore, I would like to thank all the faculty members and non-teaching staff members of the department for their wholehearted co-operation.

I would like to acknowledge the financial assistance received from University Grants Commission, Government of India under the Maulana Azad National Fellowship scheme during this time.

I am very fortunate to have a loving family to support me through these tough times. I am indebted to my husband and children for giving me enough time to myself so that I could prepare presentations and keep up with paper deadlines. I thank my parents who were always willing to help so that my work is not interrupted. I thank my parents-in-law and all my dear ones for their moral support during these years.

Simi Zerine Sleeba

**CERTIFICATE**

This is to certify that this thesis entitled "Performance and Reliability

Enhancement Techniques for Two Dimensional Network-on-Chips using

**Adaptive Deflection Routers**" is a bonafide record of the work carried out by

Ms. Simi Zerine Sleeba under my supervision in the Department of

Electronics Engineering, Model Engineering College, Kochi. The results

presented in this thesis or part of it have not been presented for the award of

any other degree(s).

I further certify that the corrections and modifications suggested by the

audience during pre-synopsis seminar and recommended by the Doctoral

Committee of Mrs. Simi Zerine Sleeba are incorporated in this thesis.

Cochin - 682021.

04-12-2017

Dr. Mini M.G.

Supervising Guide

## **ABSTRACT**

Advancements in the field of silicon process technology unveil the possibility of fabricating billions of transistors into a small chip area. Future Multi-Processor System-on-Chips (MPSoC) make use of this new trend by integrating hundreds and thousands of processing cores into a single silicon substrate. With increase in the number of on-chip processing elements, there is an ever increasing demand for a scalable and modular on-chip communication system. Network on Chip (NoC) emerges as the most suitable form of communication fabric for large MPSoCs. Extensive amount of research is being carried out on various aspects of NoCs with focus on achieving higher performance and reliability of on-chip communication. Data is transmitted in the form of packets from one processing core to another by transiting through various NoC components.

One major component of an NoC system is the router, whose architecture and algorithm play a vital role in improving the performance parameters of the NoC. From the review of recent literature on various routing techniques, it is observed that buffer-less and minimally buffered routers employing deflection technique deliver good performance and energy-efficiency simultaneously. This dissertation focuses on the study of architectural and algorithmic enhancement methods in deflection routers to improve the performance of two dimensional mesh NoCs. As NoC designs adhere to stringent power budgets, energy efficiency is also considered as an important performance measure in deflection routers. The shrinking feature size of devices fabricated on an MPSoC may cause component failures including NoC, resulting in malfunctioning of the chip. An analysis of the reliability issues due to permanent faults in two dimensional mesh NoCs and routing techniques to achieve fault tolerance is investigated in this study. Thermal imbalance due to uneven traffic distribution through the mesh network can lead to irregular wear and tear and chip failure in the long run. Hence deflection routing methods with thermal awareness are also undertaken here due to its importance.

An energy efficient deflection routing algorithm to reduce the packet deflection rate using a novel output port selection strategy is proposed in the thesis. Another approach for achieving high performance is by reducing the router delay and flit latency through single cycle router operation, which is proposed as a novel adaptive deflection router. A unique method for fault tolerant deflection routing that tolerates permanent faults in NoC components and delivers graceful performance at high fault rates is also proposed and evaluated. A new faulty router model that enhances network performance under high fault rates is also put forward. Through various evaluations, it is shown that the newly proposed methods outperform the state-of-the-art techniques in terms of network parameters and reduction of dynamic power consumption. The issue of uneven thermal distribution within a NoC is addressed by suggesting a deflection routing technique that re-routes some packets to regions with lesser traffic density.

**Keywords:** Network on Chip, Deflection routing, Performance parameters, Permutation Deflection Network, Average latency, Dynamic power dissipation, Fault tolerance, Reliability, Faulty router model, Energy efficient routing, Critical path length, Thermal variance.

## **CONTENTS**

| List        | t of Figures                           | vii  |

|-------------|----------------------------------------|------|

| List        | t of Tables                            | xiii |

| List        | t of Algorithms                        | XV   |

| List        | t of Equations                         | xvii |

| Abl         | breviations                            | xix  |

|             |                                        |      |

| 1. I        | Introduction                           | 1    |

|             | 1.1 Network-on-Chip                    | 4    |

|             | 1.2 Mesh topology                      | 5    |

|             | 1.3 Routing                            | 5    |

|             | 1.3.1 Deadlock and livelock avoidance  | 6    |

|             | 1.3.2 Buffered router                  | 6    |

|             | 1.3.3 Deflection routing               | 7    |

|             | 1.3.4 Flit format                      | 9    |

|             | 1.4 Performance parameters             | 9    |

|             | 1.5 Motivation                         | 11   |

|             | 1.6 Objectives of the research         | 12   |

|             | 1.7 Contributions of the Thesis        | 12   |

|             | 1.8 Organization of the Thesis         | 13   |

|             |                                        |      |

| <b>2.</b> ] | Related Work                           | 15   |

|             | 2.1 Buffered routing methods           | 17   |

|             | 2.2 Buffer-less routing methods        | 18   |

|             | 2.3 Minimally buffered routing methods | 21   |

|             | 2.4 Fault tolerant routing methods     | 27   |

| 2.5 Thermal aware routing methods                     | 33 |

|-------------------------------------------------------|----|

|                                                       |    |

| 3. Weighted Deflection Routing                        | 35 |

| 3.1 Weighted Deflection Buffer-less routing           | 39 |

| 3.1.1 Weighted Deflection Count                       | 39 |

| 3.1.2 Directional Weights                             | 40 |

| 3.1.3 Livelock avoidance                              | 43 |

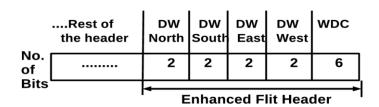

| 3.1.4 Enhanced flit header                            | 44 |

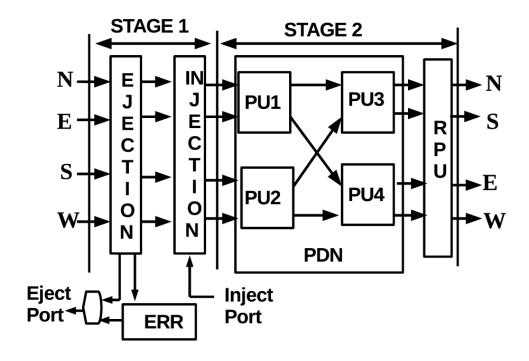

| 3.1.5 Router architecture                             | 45 |

| 3.1.6 Simulation methodology                          | 50 |

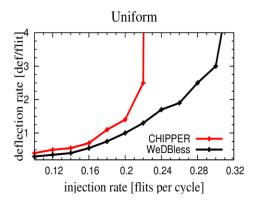

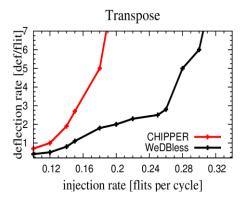

| 3.1.7 Results and discussions                         | 51 |

| 3.1.8 Hardware synthesis                              | 59 |

| 3.2 Weighted Deflection router with Minimal Buffering | 69 |

| 3.2.1 Router pipeline                                 | 60 |

| 3.2.2 Results and discussions                         | 62 |

| 3.2.3 Router timing, static power and area            | 68 |

| 3.3 Chapter summary                                   | 69 |

|                                                       |    |

| 4. High Performance Adaptive Deflection Routing       | 71 |

| 4.1 Router architecture                               | 77 |

| 4.2 Simulation methodology                            | 80 |

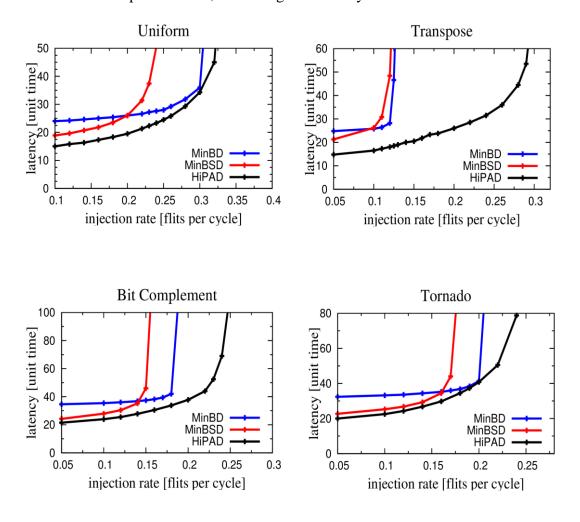

| 4.3 Results and discussions                           | 82 |

| 4.4 Router delay, static power and area               | 85 |

| 4.5 Chapter summary                                   | 87 |

| 5. Fault Tolerant Deflection Routing                  | 89 |

| 5.1 Coarse grain fault model                          | 96 |

| 5.2 Router architecture97                           |  |

|-----------------------------------------------------|--|

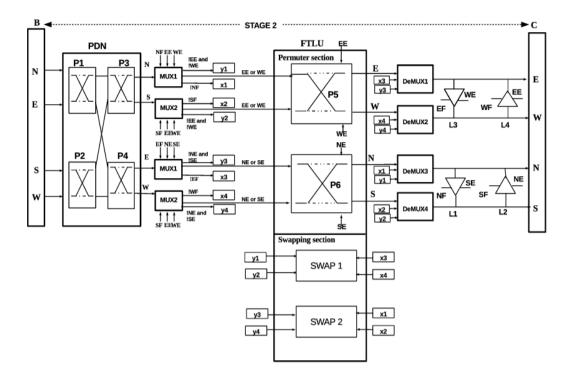

| 5.2.1 Port allocation using PDN99                   |  |

| 5.2.2 Port reallocation using FTLU99                |  |

| 5.2.3 Port reallocation using latches               |  |

| 5.2.4 Fault Loop Bit                                |  |

| 5.3 Livelock problem                                |  |

| 5.3.1 Proof of livelock freedom                     |  |

| 5.3.2 Disconnected routers                          |  |

| 5.3.3 Fault patterns with gateway routers112        |  |

| 5.4 Experimental evaluation                         |  |

| 5.4.1 Experimental methodology114                   |  |

| 5.4.2 Analysis of network level parameters116       |  |

| 5.4.3 Dynamic link power estimation121              |  |

| 5.4.4 Hardware synthesis                            |  |

| 5.5 Limitations of the coarse grain fault model     |  |

| 5.6 Enhanced fault tolerant router model            |  |

| 5.6.1 Router architecture for the enhanced model130 |  |

| 5.6.2 Side buffer parameters                        |  |

| 5.6.3 Simulation methodology                        |  |

| 5.6.4 Analysis of simulation results136             |  |

| 5.7 Chapter summary                                 |  |

| 6. Thermal Aware Deflection Routing147              |  |

| 6.1 Router Architecture                             |  |

| 6.1.1 Port Reallocation Unit                        |  |

| 6.2 Results and Discussions                         |  |

| 6.2.1 Simulation Methodology156                     |  |

| <del></del>                                         |  |

| 6.2.2 Thermal profile                | 156 |

|--------------------------------------|-----|

| 6.2.3 Thermal Variance               | 158 |

| 6.2.4 Average latency and throughput | 160 |

| 6.2.5 Real applications              | 161 |

| 6.2.6 Hardware synthesis             | 162 |

| 6.3 Chapter summary                  | 163 |

|                                      |     |

| 7. Conclusions                       | 165 |

| 7.1 Future scope of the research     | 169 |

|                                      |     |

| References                           | 171 |

| Publications                         | 183 |

| Curriculum Vitae                     | 185 |

# **List of Figures**

|            | Pa                                                              | age No. |

|------------|-----------------------------------------------------------------|---------|

| Figure 1.1 | Network on Chip in a 3x3 mesh topology                          | 4       |

| Figure 1.2 | Microarchitecture of an input buffered virtual channel router   | 7       |

| Figure 1.3 | Flit format in an 8 x 8 mesh NoC                                | 9       |

| Figure 2.1 | Sequential outport port allocation in BLESS router              | 19      |

| Figure 2.2 | Micro-architecture of CHIPPER                                   | 20      |

| Figure 2.3 | Micro-architecture of MinBD router                              | 22      |

| Figure 2.4 | Micro-architecture of MinBSD router                             | 24      |

| Figure 3.1 | Assignment of Directional Weights                               | 41      |

| Figure 3.2 | Variation of WDC with flit injection rates in an 8x8 mesh NoC   | 2 43    |

| Figure 3.3 | Format of enhanced flit header in an 8 x 8 mesh NoC             | 44      |

| Figure 3.4 | Two stage pipeline architecture of WeDBless router              | 45      |

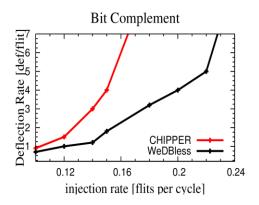

| Figure 3.5 | Average deflection rates for various synthetic traffic patterns |         |

|            | using WeDBless and CHIPPER in 8x8 mesh NoC                      | 53      |

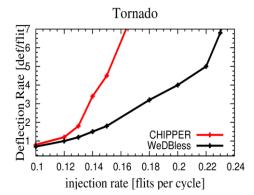

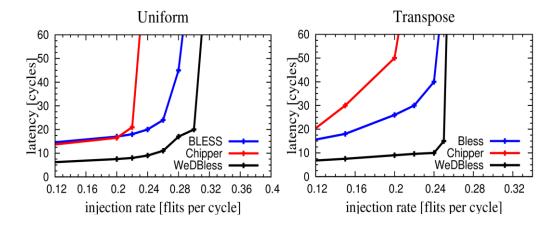

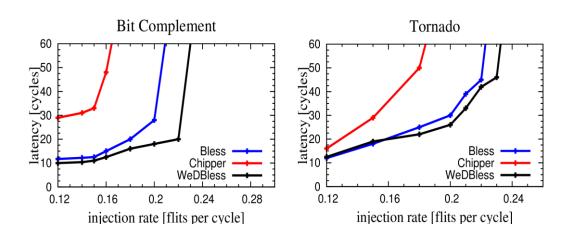

| Figure 3.6 | Average latency for various synthetic traffic patterns using    |         |

|            | WeDBless, CHIPPER and BLESS in 8x8 mesh NoC                     | 54      |

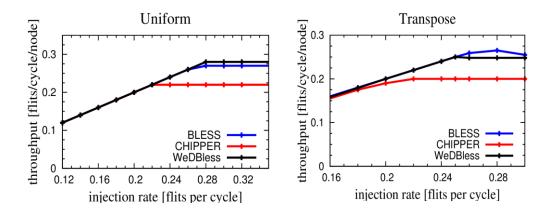

| Figure 3.7 | Average throughput for various synthetic traffic patterns       |         |

|            | using WeDBless, CHIPPER and BLESS in 8x8 mesh NoC               | 56      |

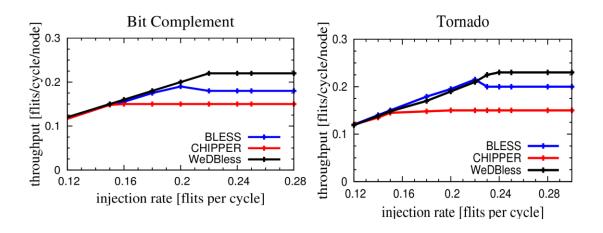

| Figure 3.8 | Percentage reduction in (a) deflection rate (b) latency of      |         |

|            | WeDBless w.r.t to CHIPPER for real workloads.                   | 57      |

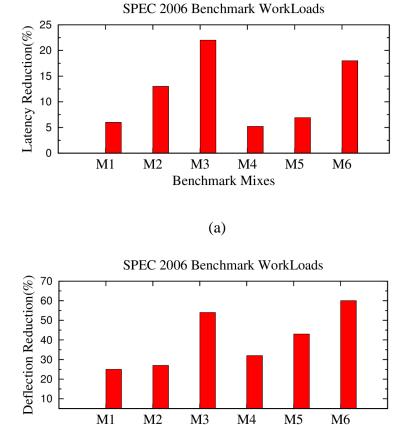

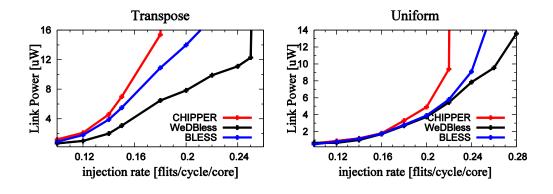

| Figure 3.9 | Dynamic power dissipation across links for various              |         |

|            | synthetic traffic patterns using WeDBless, CHIPPER              |         |

|            | and BLESS in 8x8 mesh NoC                                       | 59      |

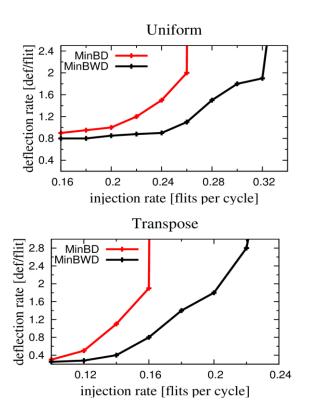

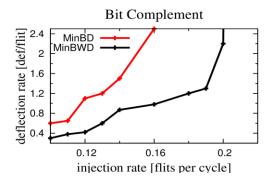

| Figure 3.10 | Two stage pipeline architecture of MinBWD router.              | 61 |

|-------------|----------------------------------------------------------------|----|

| Figure 3.11 | Average deflection rate for various synthetic traffic patterns |    |

|             | using MinBWD and MinBD in 8x8 mesh NoC.                        | 63 |

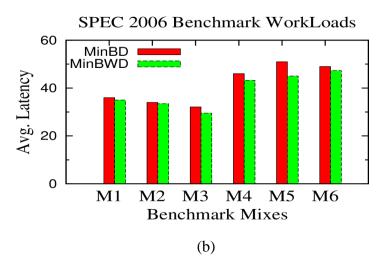

| Figure 3.12 | (a) Average deflection rate and (b) Average latency for real   |    |

|             | applications using MinBWD and MinBD in 8x8 mesh NoC            | 64 |

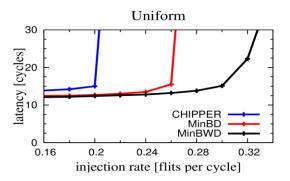

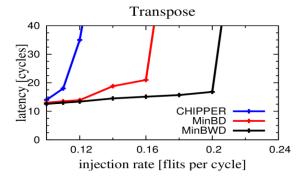

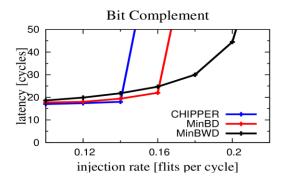

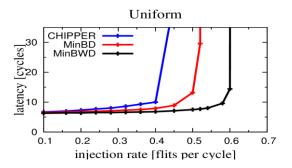

| Figure 3.13 | Average latency for various synthetic traffic patterns         |    |

|             | using MinBWD, MinBD and CHIPPER in 8x8 mesh NoC.               | 66 |

| Figure 3.14 | Average latency for various synthetic traffic patterns         |    |

|             | using MinBWD, MinBD and CHIPPER in 4x4 mesh NoC                | 67 |

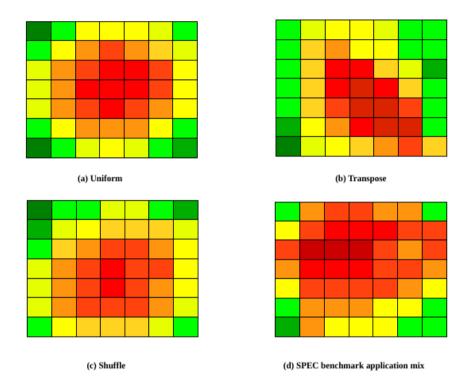

| Figure 4.1  | PDN structure of MinBSD.                                       | 75 |

| Figure 4.2  | Architecture of the proposed HiPAD router.                     | 77 |

| Figure 4.3  | PDN structure of HiPAD router.                                 | 78 |

| Figure 4.4  | Average latency for various synthetic traffic patterns using   |    |

|             | HiPAD, MinBSD and MinBD in 8x8 mesh NoC.                       | 82 |

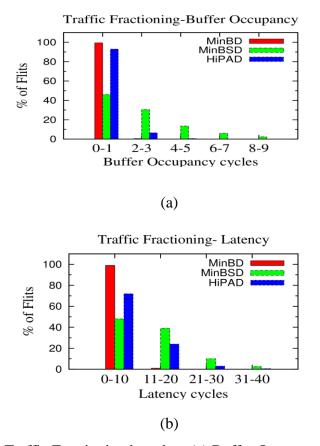

| Figure 4.5  | Traffic Fractioning based on (a) Buffer Occupancy (b) Average  |    |

|             | Latency for HiPAD and MinBSD in 8x8 mesh NoC.                  | 83 |

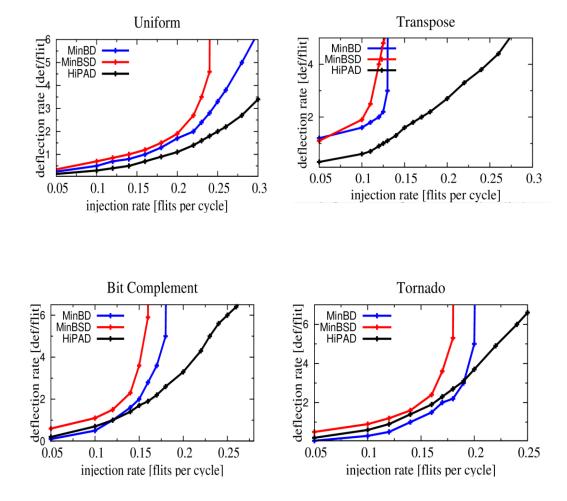

| Figure 4.6  | Average deflection rate for various synthetic traffic patterns |    |

|             | using HiPAD and MinBSD in 8x8 mesh NoC.                        | 84 |

| Figure 4.7  | Comparison of (a) Average latency and                          |    |

|             | (b) Average Deflection rate for real applications              |    |

|             | using HiPAD and MinBSD in 8x8 mesh NoC.                        | 86 |

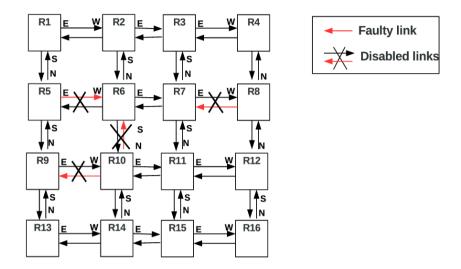

| Figure 5.1  | PDN in FaFNoC router with (a) faulty north port                |    |

|             | (b) faulty east port.                                          | 92 |

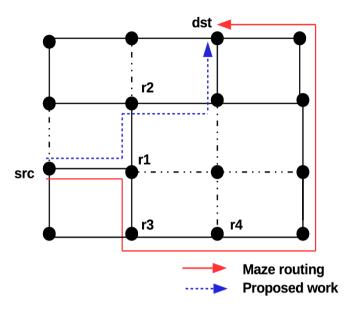

| Figure 5.2  | Demonstration of path traversed by flit from              |     |

|-------------|-----------------------------------------------------------|-----|

|             | source (src) to destination (dst) in a 4x4 mesh NoC       |     |

|             | using Maze routing and proposed work.                     | 94  |

| Figure 5.3. | Coarse grain fault model.                                 | 97  |

| Figure 5.4  | Output stage of the proposed router.                      | 98  |

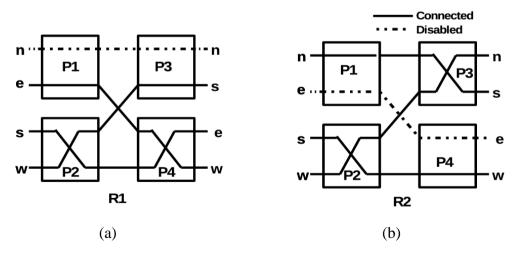

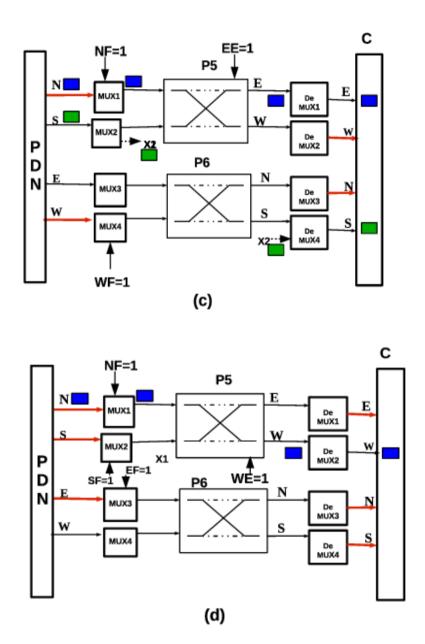

| Figure 5.5  | Reallocation of output ports in routers with              |     |

|             | (a) one faulty port (north) using permute and             |     |

|             | (b) one faulty port (north) using swap circuit and latch  | 105 |

|             | (c) two faulty ports (north and west) and                 |     |

|             | (d) three faulty ports (north, south and east)            | 106 |

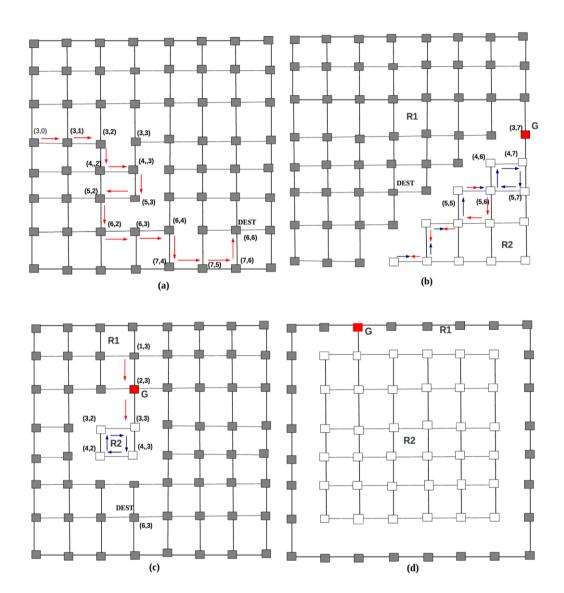

| Figure 5.6  | (a) Livelock free routing in an 8x8 mesh with multiple    |     |

|             | faults in partially distributed locations                 |     |

|             | (b), (c), (d) fault pattern dividing the network into two |     |

|             | regions R1 and R2 connected by a gateway router, G.       | 113 |

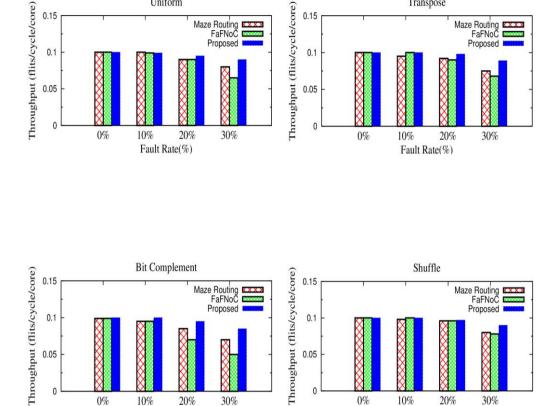

| Figure 5.7  | Average throughput Vs. Fault rate under various synthetic |     |

|             | traffic patterns for the proposed work, FaFNoC and        |     |

|             | Maze routing in $8 \times 8$ mesh NoC.                    | 118 |

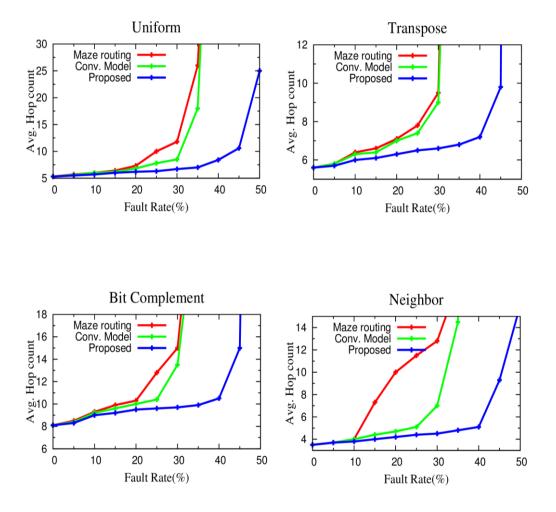

| Figure 5.8  | Average hop count Vs. Fault rate under various synthetic  |     |

|             | traffic patterns for the proposed work, FaFNoC and        |     |

|             | Maze routing in $8 \times 8$ mesh NoC.                    | 119 |

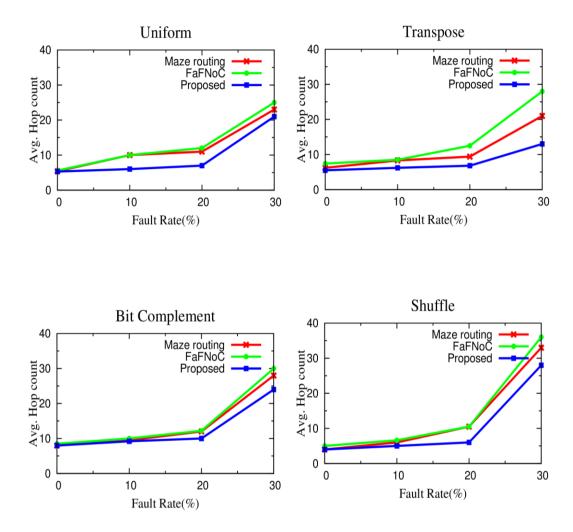

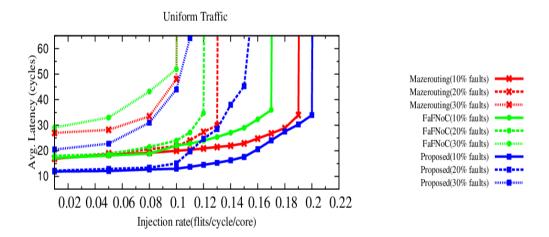

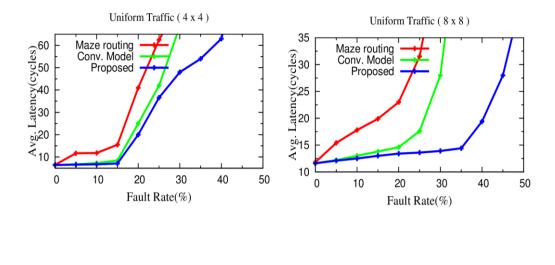

| Figure 5.9  | Average latency Vs Injection rate (uniform traffic) for   |     |

|             | various fault rates for the proposed method, FaFNoC       |     |

|             | and Maze routing in $8 \times 8$ mesh NoC.                | 120 |

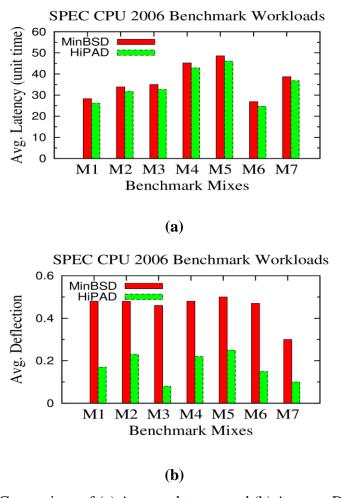

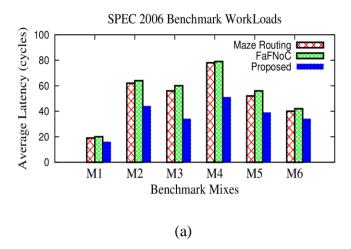

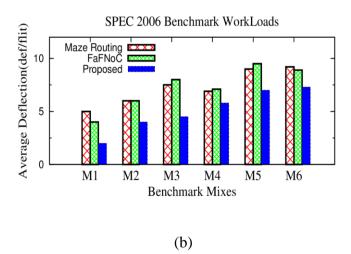

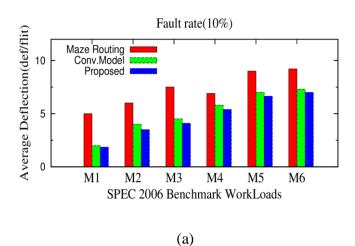

| Figure 5.10 | (a) Average Latency and (b) Deflection for 10% fault rate    |     |

|-------------|--------------------------------------------------------------|-----|

|             | under SPEC CPU 2006 benchmark applications mixes             |     |

|             | for the proposed method, FaFNoC and Maze routing in          |     |

|             | $8 \times 8$ mesh NoC.                                       | 122 |

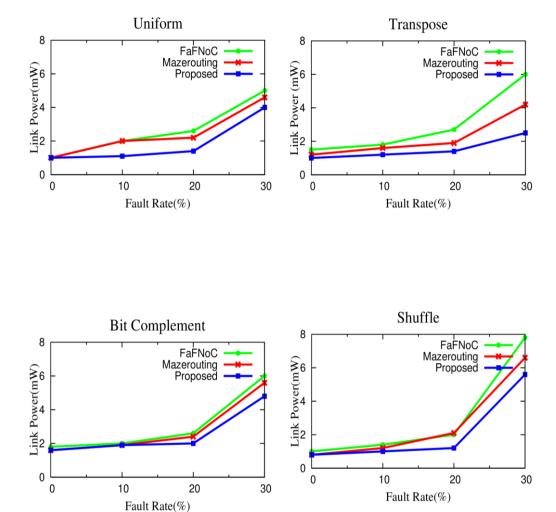

| Figure 5.11 | Link power Vs Fault rate under various synthetic traffic     |     |

|             | patterns for the proposed method, FaFNoC and                 |     |

|             | Maze routing in $8 \times 8$ mesh NoC.                       | 124 |

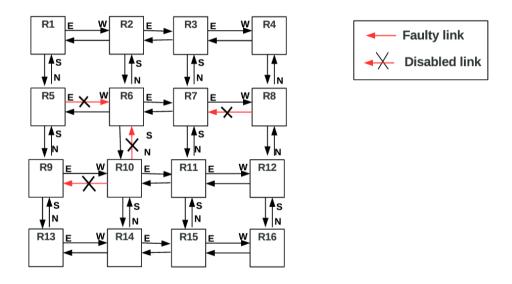

| Figure 5.12 | Representation of a 4x4 mesh NoC using enhanced              |     |

|             | fault tolerant router model.                                 | 128 |

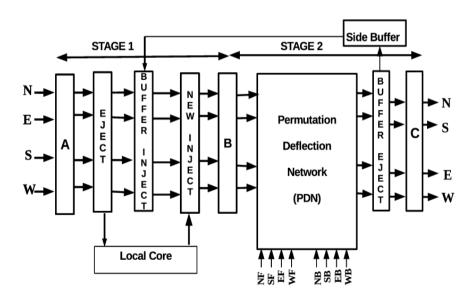

| Figure 5.13 | Two stage pipeline architecture of Enhanced                  |     |

|             | Fault Tolerant Router                                        | 130 |

| Figure 5.14 | Average hop count Vs Fault rate under synthetic traffic      |     |

|             | patterns for the proposed model, conventional model and      |     |

|             | Maze routing in 8x8 mesh NoC.                                | 137 |

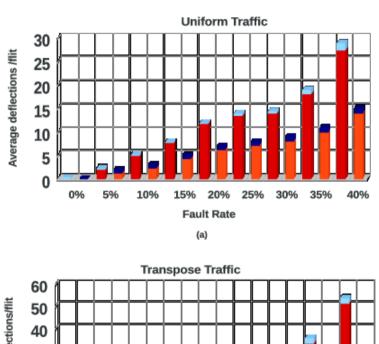

| Figure 5.15 | Average number of deflections per flit Vs Fault rate under   |     |

|             | (a) Uniform (b) Transpose traffic patterns for the proposed  |     |

|             | model and conventional model in 8×8 mesh NoC.                | 139 |

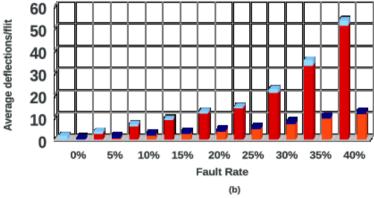

| Figure 5.16 | Average flit latency Vs. Fault rate for uniform traffic      |     |

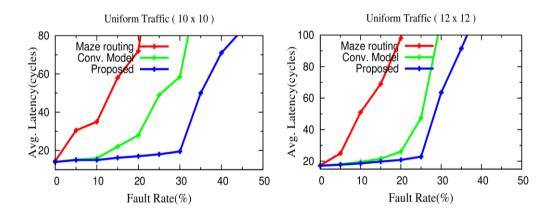

|             | pattern in 4x4, 8×8, 10×10 and 12×12 network sizes.          | 140 |

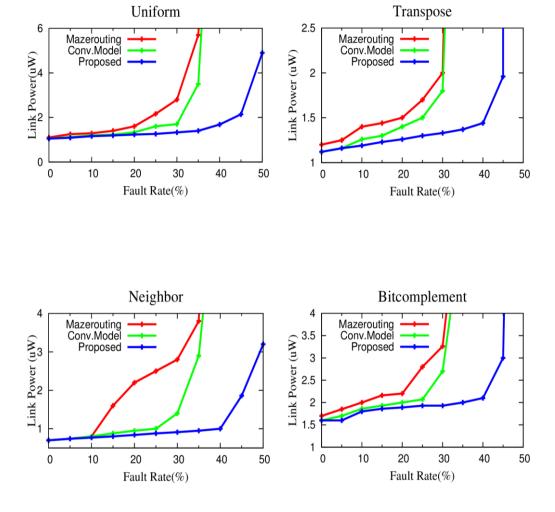

| Figure 5.17 | Dynamic Link Power (microwatts) Vs. Fault rate under         |     |

|             | Various synthetic traffic patterns for the proposed model,   |     |

|             | Conventional model and Maze routing in $8 \times 8$ mesh NoC | 142 |

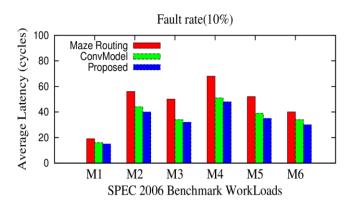

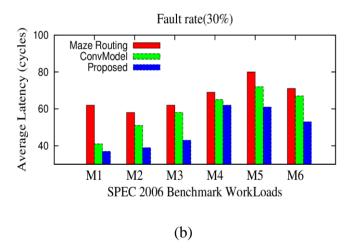

| Figure 5.18 | Average latency under various SPEC Benchmark                     |       |  |

|-------------|------------------------------------------------------------------|-------|--|

|             | application mixes for the proposed model, conventional           |       |  |

|             | model and Maze routing in an $8 \times 8$ mesh NoC with          |       |  |

|             | 10% and 30% fault rates.                                         | 143   |  |

| Figure 5.19 | Average deflection rate of flits for SPEC Benchmark              |       |  |

|             | applications in an $8 \times 8$ mesh NoC with 10% and            |       |  |

|             | 30% fault rates.                                                 | 144   |  |

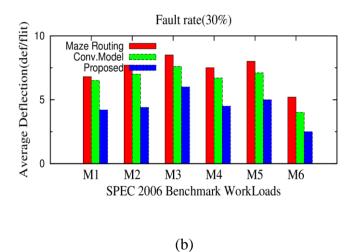

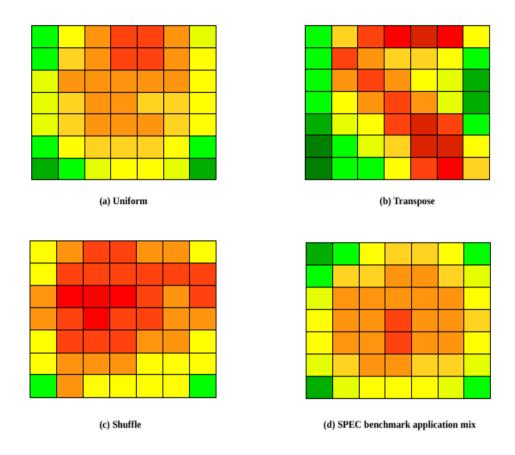

| Figure 6.1  | Thermal Profile Graph for CHIPPER in an 8x8 mesh                 |       |  |

|             | NoC using synthetic traffic patterns at pre-saturation           |       |  |

|             | injection rate.                                                  | 151   |  |

| Figure 6.2  | Two stage pipeline diagram of the proposed                       |       |  |

|             | thermal aware deflection router.                                 | 152   |  |

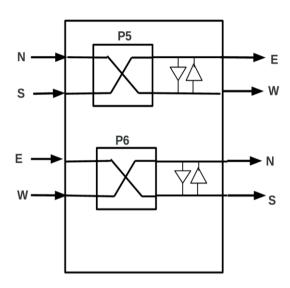

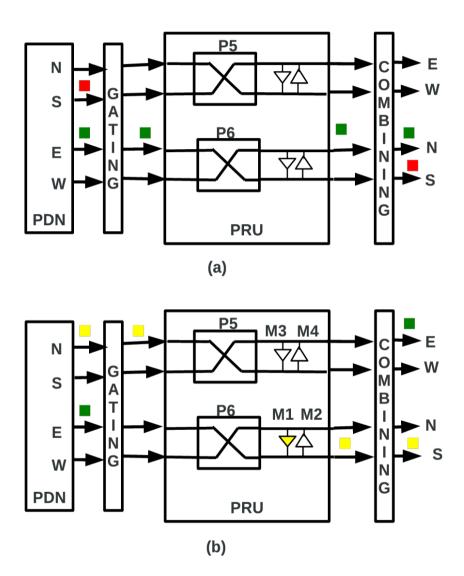

| Figure 6.3  | Structure of Port Reallocation Unit (PRU)                        | 153   |  |

| Figure 6.4  | Port reallocation using PRU                                      | 155   |  |

| Figure 6.5  | Thermal Profile Graph for an 8x8 mesh NoC with                   |       |  |

|             | the proposed router using synthetic traffic patterns at          |       |  |

|             | pre-saturation injection rate.                                   | 157   |  |

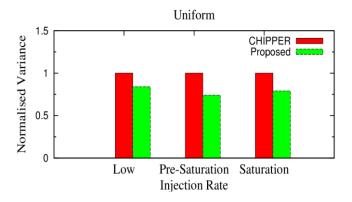

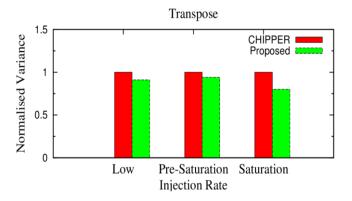

| Figure 6.6  | Normalised variance using synthetic traffic patterns for the     |       |  |

|             | proposed router w.r.t. CHIPPER in 8x8 mesh NoC                   | 159   |  |

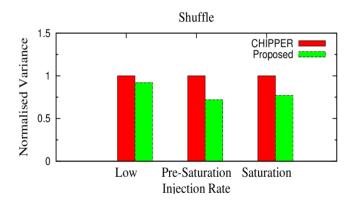

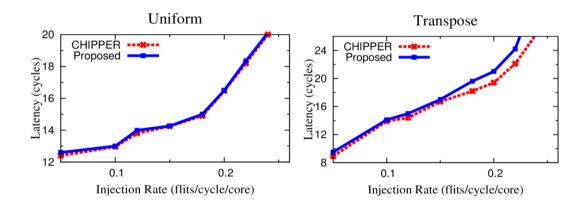

| Figure 6.7  | Average latency using synthetic traffic patterns for the propose | ed    |  |

|             | router and CHIPPER in 8x8 mesh NoC                               | 160   |  |

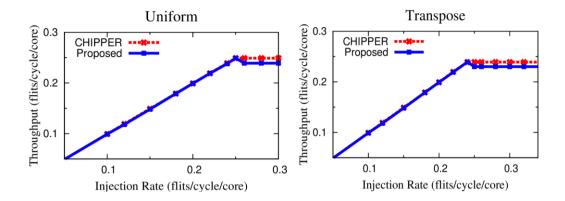

| Figure 6.8  | Average throughput using synthetic traffic patterns for the pro  | posed |  |

|             | router and CHIPPER in 8x8 mesh NoC                               | 161   |  |

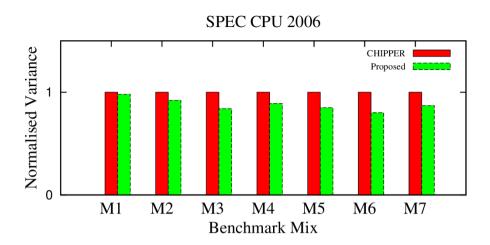

Figure 6.9 Normalised variance using applications from

SPEC CPU 2006 benchmark suite for the proposed

method w.r.t. CHIPPER in 8x8 mesh NoC

162

## **List of Tables**

|           | 1                                                                                             | Page No. |

|-----------|-----------------------------------------------------------------------------------------------|----------|

| Table 2.1 | Comparison of on chip routing techniques                                                      | 24       |

| Table 2.2 | Comparison of fault tolerant routing methods                                                  | 30       |

| Table 3.1 | Directional Weights of a router's output ports<br>for various positions of destination router | 41       |

| Table 3.2 | Current and pre-computed DWs of a flit                                                        | 49       |

| Table 3.3 | Various proportions of SPEC CPU 2006                                                          |          |

|           | applications in benchmark mixes M1 to M6.                                                     | 51       |

| Table 3.4 | Comparison of pipeline delay, area and static power                                           |          |

|           | of CHIPPER and WeDBLESS                                                                       | 59       |

| Table 3.5 | Comparison of pipeline delay, area and power of                                               |          |

|           | MinBD and MinBWD                                                                              | 68       |

| Table 4.1 | Benchmark mixes (M1 to M7) in various                                                         |          |

|           | proportions of SPEC CPU 2006 applications                                                     | 81       |

| Table 4.2 | Comparison of router delay, area and static power of                                          |          |

|           | MinBSD and HiPAD routers                                                                      | 85       |

| Table 5.1 | Various proportions of SPEC CPU 2006 applications                                             |          |

|           | in benchmark mixes M1 to M6.                                                                  | 107      |

| Table 5.2 | Router delay, static power and area for Maze router,                                          |          |

|           | FaFNoC and proposed method normalised w.r.t CHIPPE                                            | R. 125   |

| Table 5.3 | Example of flit movement through major functional                                             |          |

|           | blocks of router R10 in 5 consecutive cycles with                                             |          |

|           | side buffer size = 4 and BTI = 3 cycles.                                                      | 133      |

| Table 6.1 | Mixes (M1 to M7) of various MPKI applications                                                 |          |

# **List of Algorithms**

|               |                                      | Page No. |

|---------------|--------------------------------------|----------|

| Algorithm I   | Decision Making in HiPAD router      | 80       |

| Algorithm II  | Port Reallocation using FTLU         | 102      |

| Algorithm III | Function of a Permuter Block of PDN  | 134      |

| Algorithm IV  | Flit Buffering by Buffer Eject Block | 134      |

# **List of Equations**

|              |                                     | Page No. |

|--------------|-------------------------------------|----------|

|              |                                     |          |

| Equation 1.1 | Total latency of a flit             | 9        |

| Equation 3.1 | Link Activity Factor                | 58       |

| Equation 4.1 | Latency of a flit through a network | 76       |

| Equation 5.1 | Fault rate                          | 115      |

| Equation 6.1 | Thermal Variance                    | 158      |

| Equation 6.2 | Average                             | 158      |

## **Abbreviations**

ARIADNE Agnostic Reconfiguration In a Disconnected Network

**Environment**

BIST Built-in Self-Test

BLESS Buffer-less

BOFAR Buffer Occupancy Factor Based Adaptive Router

BTI Blocking Time Interval

CBT Core Buffer Time

CHIPPER Cheap Interconnect Partially Permuting Router

DeBAR Deflection Based Adaptive Router

DW Directional Weight

ERF Ejection Ready Flit

ERR Ejection Ready Register

FaFNoC Fault Aware Flits Network on Chip

FBP Free Buffer Priority

FIFO First-In-First-Out

FLB Fault Loop Bit

Flit Flow control unit

FTDR Fault Tolerant Deflection Router

FTDR-H Fault Tolerant Deflection Router Hierarchical

FTLU Fault Tolerant Logic Unit

GCA Global Congestion Awareness

GLB Global Load Balancing

HiPAD High Performance Adaptive Deflection Router

ITRS International Technology Roadmap of Semiconductors

LAF Link Activity Factor

LBDR Logic Based Deflection Routing

MinBD Minimally Buffered Deflection router

MinBSD Minimally Buffered Single cycle Deflection router

MinBWD Minimally Buffered Weighted Deflection router

MD Minimal and Defect Resilient routing algorithm

MOE Minimal Odd-Even

MPKI Misses Per Kilo Instructions

MPSoC Multi Processor System on Chip

MSHR Miss Status Handling Registers

NARCO Neighbour Aware turn-model based fault tolerant routing

NIC Network Interface Controller

NoC Network on Chip

PCA Proximity Congestion Awareness

PDN Permutation Deflection Network

PE Processing Element

PEF Performance Energy Fault-tolerance

RCA Regional Congestion Awareness

RPU Route Pre-computation Unit

SBOT Side Buffer Occupancy Time

SCARAB Single Cycle Adaptive Routing and Buffer-less Network

SLIDER Smart Late Injection Deflection Router

TOSR Tunnelled Overlapped Static Reconfiguration

TPG Thermal Profile Graph

VC Virtual Channel

VCR Virtual Channel Router

WeDBless Weighted Deflection Buffer-less Router

WDC Weighted Deflection Count

## **Chapter 1**

## Introduction

#### **Abstract**

This chapter commences with an introduction of the evolution of NoC as the communication medium for future multiprocessor MPSoCs. The building blocks of a NoC are described in brief and a broad classification of various routing techniques is explained. With a brief account of the parameters used for performance evaluation of NoCs, the objectives and main contributions of the research are also stated in this chapter.

The recent progress in VLSI technology and shrinking transistor geometries enable billions of such devices to be integrated on to a small silicon area. Each new generation of Multiprocessor System-on-Chip (MPSoC) takes after this trend to incorporate several hundreds of computing cores in a substrate. Homogeneous MPSoCs, also known as chip multiprocessors, consist of multiple numbers of similar processing elements. Each of these cores runs computation-intensive applications which demand huge amount of data transfer through the interconnecting communication medium. The previous generation of MPSoCs used the conventional shared bus for on chip communication because of its low cost and simple characteristics. In a shared bus, only one master can utilize the bus at a time which means that all the bus accesses should be serialized by an arbiter. As the number of processor cores increases, this mode of communication faces scalability issues due to large number of bus requests. The increase in bus length causes additional wire delay. The new trend in MPSoCs demands a paradigm shift from computation centric to communication centric designs [1]. In this context, Networks on Chip (NoC) communication is gaining widespread popularity due to its numerous advantages like scalability and modular topology which interconnects the processing elements [2]. The issue of global on-chip wire delay is tackled in NoCs by replacing them with short wires which transfer data between various processing elements. The biggest advantage of NoC is that it enables communication between multiple pairs of computing cores simultaneously.

## 1.1 Network on Chip

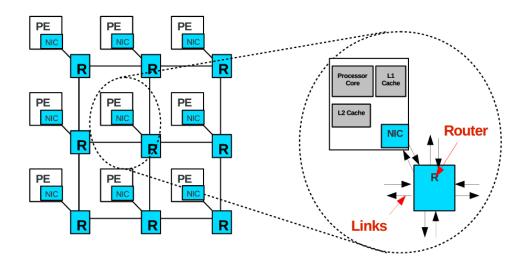

Figure 1.1 Network on Chip in a 3x3 mesh topology

Figure 1.1 shows a sample NoC with 9 Processing Elements (PE) structured as a 3x3 mesh. The main building blocks of an NoC are Network Interface Controllers (NIC), routers (R) and links between the routers. Each processing core is associated with a NIC which connects to a switching element called router. Each PE has a private L1 cache and a shared L2 cache slice. Whenever data is not found in the internal caches, a cache miss is generated and the PE requests for the data from external memory. In this case, data request packets are initiated into the network. Cache coherence transactions may also cause traffic to be injected into the NoC. In NoC, information is exchanged between various nodes in the form of packets. Typical packets are small control messages such as cache block read requests

and larger data packets contain cache block data. The NIC converts the data from the processor's native format to the NoC's packet format and vice versa.

## 1.2 Mesh topology

A two dimensional mesh is the most widely used topology for connecting PEs in an MPSoC. Each PE is connected to its local router by means of the NIC. In a mesh NoC, routers are interconnected using full duplex bidirectional links with a set of wires in each link direction. As shown in Figure 1.1, a router in a central location of the mesh is connected to its neighbouring routers in north, south, east, west directions and to the local PE using five pairs of input-ouput ports and bidirectional links. Routers at the edges and corners of the mesh have lesser number of ports and links.

## 1.3 Routing

Routing is the process of selecting optimal paths for a packet from its source to destination node. Router is considered as the most vital component which is responsible for implementing methods for flow control and congestion control in an NoC. The performance and cost of a router is primarily dependent on its microarchitecture. The routing algorithm is realized using various functional units arranged in a pipelined structure inside the router. The degree of adaptability of a routing algorithm is determined by its capability to forward packets along the network in a distributed manner. A major challenge faced by researchers is to design routing algorithms that deliver high network performance and energy efficiency in compliance with the power and area constraints of the chip. Efficient routing protocols should also ensure reliable

delivery of packets to their destinations when the default routes fail. Uniform traffic distribution is yet another aspect to be considered by the routing function to prevent uneven hotspots in specific chip areas such as the centre of the chip.

#### 1.3.1 Deadlock and livelock avoidance

Deadlock is a state when packets wait for each other in a circular fashion but none of the packets are able to move in the network. Livelock refers to a state in which the packets are able to make progress but they are unable to reach their destination, thereby flowing in the network without getting ejected to their destinations. The routing algorithm should ensure that packet transmission through the network is free from deadlock and livelock.

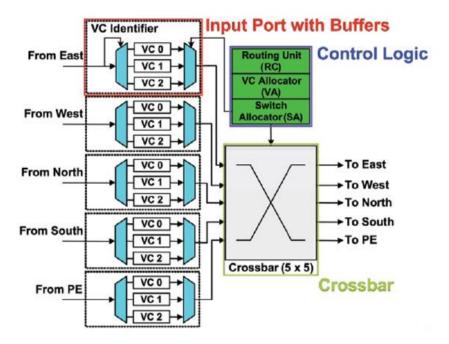

#### 1.3.2 Buffered router

Conventional routers employ a large number of buffers at the input ports so that packets belonging to different packet transmissions can proceed simultaneously through the same physical channel [3, 4]. In a Virtual Channel Router (VCR), each physical channel is shared by several virtual channels. The microarchitecture of a conventional VCR is shown in Figure 1.2. Packets that cannot be forwarded immediately through desired output ports of a router are temporarily held in FIFO buffers at the input ports till they can proceed further. Usage of these buffers prevents unnecessary wastage of link bandwidth and increases the network saturation point. But these buffers consume significant amount of dynamic power when active and static power when idle [5, 6]. In the Intel Terascale 80-core chip, 28% and for MIT RAW, 36% of chip power is consumed by the NoC [7, 8]. In the TRIPS prototype chip, input buffers of the

Figure 1.2 Microarchitecture of an input buffered virtual channel router [4].

routers were reported to occupy 75% of the total on-chip network area [9]. Hence buffer size is an important parameter that affects area, power and performance of NoCs.

## 1.3.3 Deflection routing

VCRs provide an overprovisioned buffer size to accommodate the worst case network traffic. Unlike synthetic traffic patterns used for experimental purposes, packet injection rate is found to be very low for real applications;

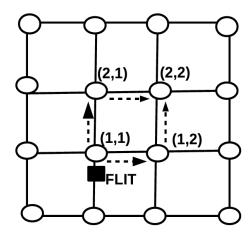

hence buffer utilization is very less [10]. In buffer-less deflection routers, the input buffers used in VCRs are completely eliminated and packets are forwarded using deflection routing mechanism [5], [11]. The concept of bufferless deflection routing has gained wide acceptance as it is capable of delivering performance similar to its buffered counterpart along with significant reduction in power consumption. Packets are split up into flow control units called flits [3]. A router receives flits coming from north, south, east and west directions and also from the processing element connected to it. Flits are introduced into the network from the local processing core through the injection process and flits are removed from the network into its destined processing core by the ejection process. In buffer-less deflection routers, when more than one incoming flit competes for the same output port, one wins and traverses through the desired output port, the others are assigned non-productive ports i.e. such flits are deflected. A necessary condition for buffer-less deflection routing is that the router should have equal number of input and output ports. This ensures that all the flits entering the router move out through the output ports at the end of the router pipeline. Since buffers are not used, this routing mechanism saves power and chip area significantly.

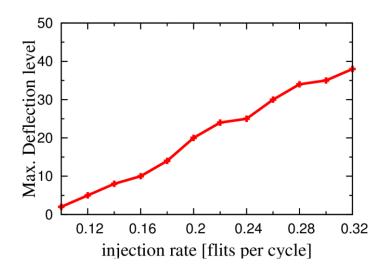

Movement of flits in unproductive directions through the links is termed as deflection. The deflection rate of flits becomes very high at high traffic injection rates and this leads to early saturation of the network compared to buffered routers. As an effort to reduce the flit deflection rate, minimally buffered routers use a small side buffer to store a fraction of the deflected flits [10]. This arrangement helps to achieve performance levels similar to that of NoCs with buffered routers. At the same time, the area and power consumed by the side buffers is negligible compared to that of VCRs. In this dissertation, the

various factors affecting the performance and energy efficiency of deflection router based NoCs is being investigated.

#### 1.3.4 Flit format

The source and destination nodes of a flit are determined by the PE from which it originates. Each flit is routed independently i.e. routing information such as the source and destination addresses are included in the header part of the flit. The typical format of a flit in an 8 x 8 mesh NoC is shown in Figure 1.3. The number of bits that are physically transmitted simultaneously through a NoC link determines the link width. In deflection routers, the link width is equivalent to the number of bits of a flit.

Figure 1.3 Flit format in an 8 x 8 mesh NoC

## 1.4 Performance parameters

Packet latency is the most frequently used parameter for measuring the performance of an NoC. Average latency is defined as the average number of clock cycles (average time) taken by flits to reach from source to destination. In a deflection router based NoC, total latency of a flit is given by equation 1.1.

$$L_T = L_I + L_R + L_L$$

-- (1.1)

#### where

L<sub>T</sub> - Total latency of a flit

L<sub>I</sub>. Flit Injection latency

L<sub>R</sub> - Latency at the routers

L<sub>L</sub>- Latency at the NoC links

The flit injection latency,  $L_{\rm I}$  is the time for which flits generated by a PE wait in its core buffer before being admitted into the network. Injection latency increases with network congestion, since flits have to wait for longer time in the core buffer to enter into the network through a vacant flit channel [12]. In NoCs using deflection routing mechanism, latency of a flit through a link is one cycle. Hence, total latency through the links,  $L_{\rm L}$  is equal to the number of hops made by the flit during its traversal.

Each hop through the link either results in a progressive step in the direction of the flit's destination or a deflection in an unwanted direction. The latency experienced by flits in the links can be optimized by reducing these deflections using smart and adaptive routing techniques. Hence, average deflection rate and hop count of flits are also considered as important performance criteria for deflection router based NoCs. The traversal of flits through the links leads to dynamic power dissipation which is directly proportional to the average hop count in the network. An NoC should be designed within specific power limits and minimization of dynamic power wastage across the NoC links due to flit deflections helps to achieve better energy efficiency.

Another commonly used performance parameter is average throughput which is defined as the rate at which packets are delivered by the network per router. For a buffer-less deflection router based NoC, the throughput of the network is equivalent to the packet injection rate. Increase in the injection rate leads to growing congestion in the network and the network subsequently moves into a saturation state. Beyond saturation level, the network congestion is extremely high and flit injection latency rises up. Accordingly, the rise in average throughput slows down and approaches a steady value..

Performance enhancement can also be achieved by optimizing the router latency,  $L_{R.}$  By smart allocation of output ports inside a router, flits can be routed through less congested and minimal paths to their destinations. Router latency can also be minimized by using routers with single cycle delay.

### 1.5 Motivation

With performance enhancement and increase in complexity of multi core systems, the power consumption also increases linearly [1]. Routing protocols have a significant impact on performance and power of NoC based MPSoCs. Buffer-less routers with deflection routing is used in NoCs to reduce the power consumed by the traditional input buffered VC routers. Though a few efficient deflection routers have been proposed previously, their architectural and algorithmic limitations result in heavy deflection and increased latency of flits in the network. As a result performance is throttled and dynamic power is wasted. Hence there is a high demand for developing high performance and energy efficient deflection routing techniques. Reliability of the chip due to permanent failure of NoC components is another issue which needs to be researched.

Deflection routers need to incorporate fault tolerant logic which minimise power and area overheads while delivering graceful performance. Another area of concern is the non-uniform thermal distribution across the chip arising from uneven network traffic which affects the long term reliability of the chip. Effective solutions to the performance and reliability issues in deflection router based NoCs are proposed in this thesis.

## 1.6 Objectives of the research

Efficient deflection routing mechanisms that maximize the performance metrics while providing high adaptability to network congestion, high fault resilience and an even thermal distribution are most desirable. The various aspects that limit the performance of two dimensional mesh Networks-on-Chip are investigated in this thesis and architectural and algorithmic techniques are developed which aim at enhancing its

- Performance parameters

- Energy-efficiency

- Fault tolerance

- Uniform thermal profile

## 1.7 Contributions of the Thesis

The main contributions of this dissertation are listed as follows.

- Proposed an energy efficient routing algorithm based on weighed deflection routing that successfully reduces the deflection rate of flits in buffer-less and minimally buffered deflection router based NoCs.

- Proposed an adaptive deflection router with single cycle delay that achieves higher speed of operation and reduced deflection rates.

- Proposed a fault tolerant technique using deflection routers in two dimensional mesh NoCs which delivers significantly high network performance for high fault rates in NoC components. An enhanced model of a faulty router that improves the availability of fault-free links in the network is also developed.

- Developed an adaptive deflection routing technique that re-routes deflected flits away from the centre of the mesh network to obtain an even thermal distribution throughout the NoC.

# **1.8 Organization of the Thesis**

Chapter 1 presents an introduction to the thesis along with the main objectives, background concepts and author's contributions.

Chapter 2 provides a systematic review of previous research on various routing methods with emphasis on adaptive deflection routing techniques for high performance and energy efficiency. It also discusses literature related to fault tolerance mechanisms adopted in NoC routers. Various load balancing techniques and congestion aware routing methods are also presented here.

Chapter 3 describes a novel output port selection strategy in NoC routers using a weighted deflection routing. The proposed method is evaluated on buffer-less and minimally buffered deflection router based NoCs of various sizes. The impact of the new scheme on NoC performance parameters and dynamic power dissipation are analysed by comparison with state of the art techniques.

Chapter 4 analyses the factors that limit the performance of a recent single cycle routing technique. An new architectural modification is proposed to overcome identified problems like structural isolation. Experimental analysis of the proposed scheme and comparison with earlier work is provided in the latter half of the chapter.

Chapter 5 presents a novel fault tolerant deflection router. The proposed architecture and routing algorithm is explained in detail followed by the experimental evaluation of the proposed scheme at various fault rates. An enhanced fault tolerant router model is also explained with evaluation results...

Chapter 6 presents a thermal aware routing scheme to attain uniform thermal profile across the mesh NoC using deflection re-routing method. Analysis of experimental results of the proposed method is also conducted and compared with the baseline methods at the end.

Chapter 7 concludes the thesis with a summary of the proposed techniques and a brief account of the potential for future research.

# **Chapter 2**

# **Related Work**

### **Abstract**

This chapter presents a detailed review of previous literature related to router architectures and routing algorithms for NoCs. Beginning with buffered routing techniques, various deflection routing methods for achieving high performance and energy efficiency are discussed. Wide range of techniques that incorporate fault tolerance feature in deflection router based NoCs are studied. Various adaptive routing techniques for congestion avoidance and load balancing are also reviewed.

The main attributes of an NoC are topology, routing and flow control. Efficient methods in each of these aspects are desirable in achieving high network performance and energy efficiency. Routers are considered as the most vital components of an NoC as they incorporate various logic blocks for implementing routing algorithms and flow control methods. This chapter presents a comprehensive survey of various state-of-the-art routing techniques for performance and reliability enhancement in two dimensional NoCs.

NoC routers are broadly classified into buffered and buffer-less domains.

## 2.1 Buffered routing methods

Buffered routers are the conventional routers with buffers at the input side. The concept of multiplexing a single physical channel over several logical channels with independent buffer queues is implemented using the concept of virtual channels. Packets belonging to different transmissions occupy different virtual channels and make progress through the router by sharing the physical channels [4]. Wormhole routing is a flow control method in which only the first flit of each packet contains the header information (head-flit) and all subsequent flits simply follow the preceding flit [3]. This method is largely adopted in VC routers because of minimal buffer requirements and good channel utilization. A flow control scheme which utilises the existing pipelined channels as storage in place of explicit virtual channel buffers is proposed in [13]. A routing approach based on virtual circuits that can be established and broken dynamically according to the network conditions is proposed in [14]. Despite the capability of buffered routers to deliver high network performance, buffers are subject to high energy dissipation both in active and idle states [5].

Buffers also consume significant portion of the router area. Some of the past works mitigate buffer size and maximise its utilization by novel methods like dynamic buffer utilisation and leakage aware buffers with power supply gating for unused buffers [15, 16].

A routing algorithm consists of the logic that selects an output port for a flit arriving at the router's input on the basis of the destination address contained in the flit header. In a deterministic routing algorithm, the routing path between a pair of nodes in the network is fixed. One of the most commonly used deterministic routing algorithms for mesh topology is XY routing, where a packet first moves along the row and then along the column to reach the destination [17]. Adaptive routing algorithms, on the other hand, choose alternate paths for packets if original paths in the network are congested. Adaptive methods like dynamic XY routing are more suitable for attaining improved network performance while tolerating failures in routers and links [18, 19]. Other metrics like free buffer slots or virtual channels are also used by adaptive algorithms for congestion aware routing [20-23]. Another aspect of NoCs with buffered routers is to ensure deadlock and livelock safety of flits. Minimal Odd Even routing (MOE) is a popular deadlock free routing algorithm that prohibits flits from making certain turns during their hop to destination [24].

## 2.2 Buffer-less routing methods

Buffer-less routers have evolved as an energy efficient solution for on chip networks [5]. SCARAB is one of the first generation routers that handle the port allocation problem without using any buffers [25]. It uses the method of

dropping and re-transmission of packets which are unable to obtain an output port in a productive direction. A separate circuit switched network is maintained to send negative acknowledgements about the discarded packets. As the packets should anticipate retransmission, they are stored in the Miss Status Handling Registers (MSHR) of the processor till a positive acknowledgement is received. Due to high retransmission overheads and requirement of separate networks for data packets and acknowledgements, this approach is not suitable for simple, low power NoC. Deflection routing is the most popular mechanism used in buffer-less routers as it does not incur such overheads.

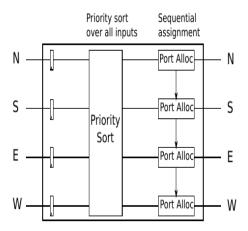

Figure 2.1: Sequential output port allocation in BLESS router [5].

A buffer-less router, BLESS proposes a deflection routing mechanism in which flits arriving at the router's input ports are allocated to one of the output ports after passing through various functional blocks inside the router [5]. Flits are sorted on the basis of age and port allocation unit in the router allocates the output ports in oldest first order. The schematic diagram in Figure 2.1 depicts

the sequential output port allocation in BLESS. As a result of sequential port allocation, the critical path length of the router increases. In order to accommodate the lengthy router operation, a wider clock pulse is required. This results in lowering of the operating frequency of the NoC.

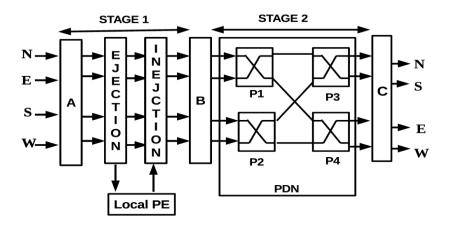

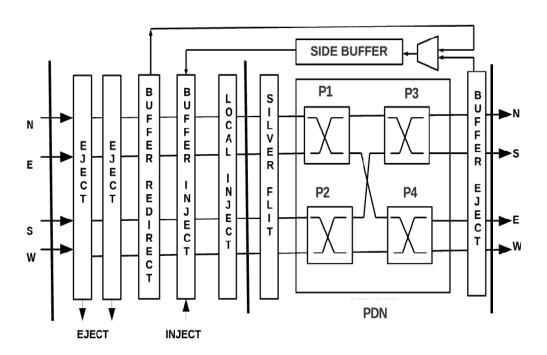

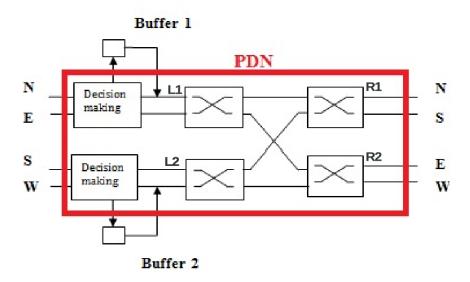

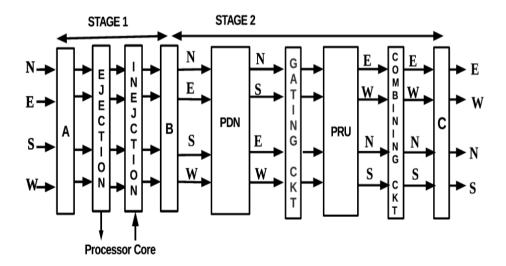

A superior deflection router architecture is that of CHIPPER (Cheap Interconnect Partially Permuting Router) which employs parallel port allocation of flits, thereby reducing its critical path length [11]. The router pipeline of CHIPPER is shown in Figure 2.2. The output port allocator, which is referred to as the Permutation Deflection Network (PDN), consists of four permuter blocks arranged in two stages, each stage having two blocks. P1 maps flits from the north and east inputs to one of its output lines connected to P3 or P4. P2 does the same operation in parallel for flits from south and west input lines. Permuters P3 and P4 connect each of the input flits from P1 and P2 to one of the four output ports. Even though parallel operation makes CHIPPER faster compared to BLESS, it exhibits higher flit deflection rate due to the inefficiency of the flit prioritization scheme.

Figure 2.2: Micro-architecture of CHIPPER [11].

The logic functions in BLESS and CHIPPER are divided into two stages and each stage has a delay of one clock cycle; hence the total delay of flits in each router is two clock cycles. A deflection routing for hierarchical mesh NoCs that uses a high radix crossbar to reduce the number of routers is presented recently [26].

Deflection routing is inherently free from deadlock since the router's resources are not withheld by flits for more than one cycle. However, routing algorithms need to incorporate sufficient mechanisms to guarantee livelock freedom of flits. Sequential allocation of output ports to flits in oldest first order is used for resolving livelock issue in BLESS [5]. This technique ensures that the older flits in the network reach their destinations early. CHIPPER proposes a scheme which marks a flit as the highest priority flit in the entire network [11]. This flit which is termed as the golden flit is guaranteed to occupy productive output ports in each router and reach its destination through the shortest path. Then the golden token is passed to another flit that is next in age order in the network.

## 2.3 Minimally buffered routing methods

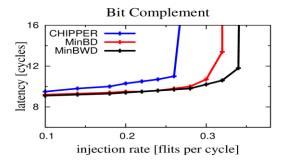

MinBD (Minimally Buffered Deflection router) is the first router to use side buffering technique to overcome the disadvantage of CHIPPER i.e. high deflection rate [10]. The microarchitecture of MinBD router shown in Figure 2.3 has functional units similar to that of CHIPPER arranged as two pipeline stages. The buffer eject unit at the end of the router pipeline picks one of the deflected flits from the output channels of the PDN in each cycle and stores it in a side buffer temporarily. The buffered flits re-enter into the router pipeline

in a subsequent cycle through any of the vacant input channels following first-in-first-out (FIFO) policy. The size of the side buffer is insignificant compared to the virtual channel buffers; hence they cause very less impact on router power and area. For improving the efficiency of the livelock safety mechanism, MinBD uses a local flit priority in addition to the golden prioritisation scheme introduced in CHIPPER. One among the four flits in the input channels of a MinBD router is marked as high priority flit (silver flit), which is given preference to obtain an output port of its choice during port allocation by the

PDN.

Figure 2.3: Micro-architecture of MinBD router [10].

DeBAR uses a minimal central buffer pool to store some of the misrouted flits [27]. It dynamically controls the flit injection from local core and the central buffer pool to ensure fairness and exhibits promising results compared to MinBD. In both MinBD and DeBAR routers, injection of flits from the local processor and side buffer takes place before output port allocation. Here, there is a path for the newly injected flits to move to the side buffer. SLIDER proposes a router architecture in which injection occurs after port allocation [28]. It reduces the problem of channel wastage and intra-router interval occurring in MinBD and DeBAR. Another router with buffer-less wormhole routing which uses a register array to store flits temporarily is proposed in [29]. The study of various NoCs using deflection routing comes out with the opinion that a priority based deflection policy which uses global or history related criteria is most suited for boosting the performance of networks [6]. MinBD, DeBAR and SLIDER incur a pipeline delay of two clock cycles.

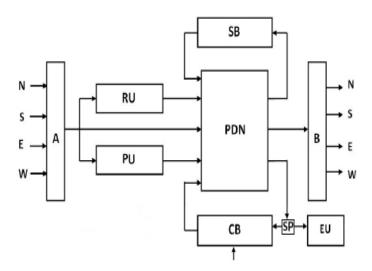

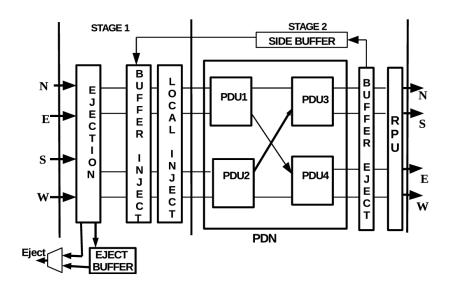

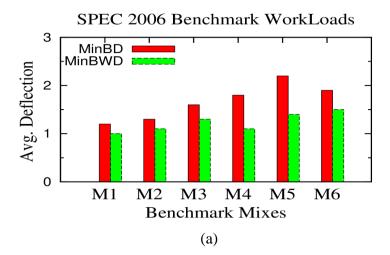

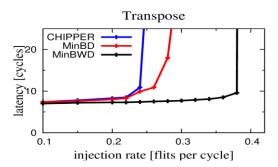

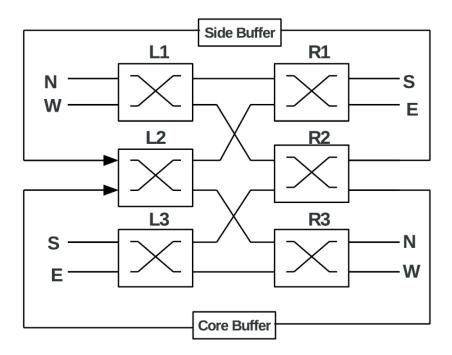

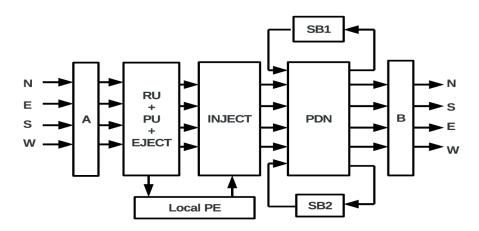

As mentioned in equation 1.1, a method for improving the performance of NoC is by reducing the router delay. Some deflection routers achieve high performance by completing the routing operation in a single clock cycle [25],[30]. A recently proposed work in this domain is Minimally Buffered Single Cycle Deflection router (MinBSD) [30]. The microarchitecture of MinBSD router is shown in Figure 2.4. The length of the router pipeline is reduced by parallelisation of independent operations like route computation (RU) and flit prioritisation (PU). MinBSD uses a derivative of the two stage PDN proposed in CHIPPER, each stage having three permuter blocks to interconnect the input ports, two side buffers, SB and CB and four output ports. The two side buffers store a minimum number of misrouted flits and one of them also stores flits generated by the local processing core.

Figure 2.4 Micro-architecture of MinBSD router [30].

Table 2.1 Comparison of on chip routing techniques

| Proposed<br>Method | Routing method | Router<br>delay<br>(cycles) | Output<br>port<br>allocati | Merits        | Limitations  |

|--------------------|----------------|-----------------------------|----------------------------|---------------|--------------|

|                    |                | (-3)                        | on                         |               |              |

| Wormhole           | Wormhole       | 4                           | Crossba                    | Channel       | Head of line |

| router [3]         | routing        |                             | r                          | bandwidth     | blocking,    |

|                    |                |                             | switchi                    | is flit size, | deadlock     |

|                    |                |                             | ng                         | Reduced       | occurence    |

|                    |                |                             |                            | buffering     |              |

| VCR [4]            | Wormhole       | 4                           | Crossba                    | Deadlock      | Each virtual |

|                    | routing        |                             | r                          | free          | channel      |

|                    |                |                             | switchi                    | channel       | requires     |

|                    |                |                             | ng                         | sharing       | buffer space |

|                    |                |                             |                            | among         |              |

|                    |                |                             |                            | various       |              |

|                    |                |                             |                            | packets       |              |

|                    |                |                             |                            | _             |              |

|                    |                |                             |                            |               |              |

| BLESS [5]       | Buffer-less<br>deflection<br>routing           | 2 | Sequent                       | No input<br>buffers,<br>low static<br>and<br>dynamic<br>power                                      | Low<br>performance<br>at high<br>injection rate,<br>Low speed of<br>operation |

|-----------------|------------------------------------------------|---|-------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| CHIPPER<br>[11] | Buffer-less<br>deflection<br>routing           | 2 | Parallel<br>using<br>PDN      | Fast<br>operation                                                                                  | High deflection rate and dynamic power dissipation                            |

| MinBD [10]      | Minimally<br>buffered<br>deflection<br>routing | 2 | Parallel<br>using<br>PDN      | Low deflection rate and high throughput                                                            | Inefficient flit<br>prioritisation                                            |

| MAS [29]        | Buffer-less<br>wormhole<br>routing             | 2 | Crossba<br>r<br>switchi<br>ng | Lower latency and receiver side buffering compared to BLESS-Worm                                   | Buffers required in routers to store flits temporarily.                       |

| DeBAR [27]      | Minimally<br>buffered<br>deflection<br>routing | 2 | Parallel<br>using<br>PDN      | Minimal central buffer pool, ensures fairness to flits from buffer, higher performan ce than MinBD | Channel wastage, unnecessary internal flit movement                           |

| SLIDER [28]    | Minimally<br>buffered<br>deflection<br>routing | 2 | Parallel<br>using<br>PDN  | Reduced channel wastage and intra-router interval, higher performan ce than DeBAR | Requires two cycles to complete operation                                       |

|----------------|------------------------------------------------|---|---------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| SCARAB<br>[25] | Buffer-less<br>packet<br>dropping              | 1 | Parallel<br>allocato<br>r | High<br>frequency<br>of<br>operation                                              | Acknowledge<br>ment network<br>and packet<br>retransmissio<br>n overheads       |

| MinBSD [30]    | Minimally<br>buffered<br>deflection<br>routing | 1 | Parallel                  | High<br>Speed, no<br>dropping<br>of packets                                       | Poor<br>structural<br>connectivity<br>Penalisation<br>of high<br>priority flits |

Table 2.1 summarises the merits and demerits of various on-chip routing techniques. More emphasis is given to the study of deflection routing techniques because of their utility in energy efficient interconnect design. Studies reveal that architectural and algorithmic modifications to the existing bufferless baseline, CHIPPER and minimally buffered MinBD can help in further enhancing the performance parameters of the NoC.

## 2.4 Fault tolerant routing methods

A wide range of routing techniques for the detection, diagnosis and tolerance of faults in two dimensional NoC systems has been analysed. Two types of faults may occur in NoCs, transient and permanent. Transient faults (soft errors) are caused due to unpredictable reasons like voltage induced delay, radiation induced fluctuations or crosstalk [31]. These types of faults are mostly handled using flow control mechanisms and error control coding schemes like cyclic redundancy check and parity codes [32]. An end to end error correction and retransmission scheme is recently proposed in [31]. Another recent work integrates error detection into the input ports of routers and correction of errors is provided at the network interfaces [33]. On the other hand, device wear out or manufacturing defects may cause permanent failure in chips [34]. Online detection of permanent faults using error syndrome collection is presented in [35]. A Built-in Self-Test (BIST) unit is embedded into each router to diagnose the faults in the Vicis NoC, which makes it a costly solution [36].

In general, permanent faults are tolerated by utilizing the redundant structure of NoC and fault tolerant algorithms that route packets around faulty components. Faulty links and routers in NoC are represented using architectural level fault models. Majority of the prior work use a coarse grained fault model which deactivates a pair of bidirectional links corresponding to a fault in a single direction [37, 38]. Both faulty and fault-free routers in the resultant network consist of only bidirectional links which makes it easy to explore at least one deadlock-free route for a flit. Many of the fault-free unidirectional links cannot be utilized for transmitting flits in this model, this

results in shrinking of available bandwidth with increase in fault rates. A fault tolerant NoC with dynamically configurable bidirectional links is used to tolerate static and dynamic faults [39]. In fault models using high levels of abstraction, routers with faulty logic blocks are modelled by disabling all input-output links to it. Vicis improves upon the coarse-grained model by mapping gate-level failures within the router to a fault in one of the bidirectional links [40]. Immunet reserves an escape virtual channel inside each router for packets that encounter faulty links in their path [38]. In some of the recent papers, hardware faults are included with finer granularity and mapped to a corresponding high level abstraction fault [41, 42].

In uDirec, a fine grained fault model is presented, in which a failure in a router's datapath element is mapped to a fault in one of the unidirectional links [41]. Faults in control circuit elements are fatal to router operation; hence such errors are modelled by marking all input-output ports of the router as faulty. Apart from the commonly used performance parameters, the Performance-Energy-Fault tolerance (PEF) metric is used for evaluating a faulty NoC. In uDirec, one of the nodes is designated as a supervisory node which keeps track of the healthiness of routers and links. On detecting a fault, this node runs a reconfiguration algorithm to update the routing tables according to the newly evolved topology. The reconfiguration phase usually consumes many cycles and normal router operation is stalled during this period. uDirec is reported to incur high reconfiguration overhead and large area overhead whereas TOSR achieves fast reconfiguration [41],[43]. Such centralised approaches involve an additional risk of the supervisory node becoming faulty which might cause the entire chip to fail [44 - 46].

On the contrary, distributed methods achieve fault tolerance by local decision making at each router [37], [47-49]. A virtual channel based routing technique with low fault coverage is presented in [50]. Fault-tolerant routing algorithms that provide deadlock freedom based on the turn model are proposed in [47], [51-54]. A fault resilient algorithm that works on dynamic reconfiguration of routes is presented in [52]. Hermes [53] adopts dimension order routing or up/down routing based on routing tables whereas NARCO [54] uses a region based fault awareness approach for achieving high throughput. A novel fault tolerant routing approach which avoids virtual channels and utilises acyclic channel dependency graph for deadlock avoidance and connectivity is presented in [55].

The coarse-grained fault model is widely used in deflection routers since all routers have equal number of input and output ports. Most of the deflection routers are equipped with built-in fault tolerant logic. In the presence of faults, routing decisions are made locally at each router; hence reconfiguration is very fast [48, 49]. FTDR-H is a deflection routing method with high fault coverage but consumes large area due to routing tables [49]. Some adaptive routing algorithms make routing decisions based on various cost functions like route length, local fault status or two hop fault information [56, 57]. Recently proposed methods employ the PDN proposed in buffer-less CHIPPER [11] and minimally buffered MinBD [10] for output port allocation of flits. In the Fault Aware Flits based NoC (FaFNoC), fault tolerance is achieved by disallowing some connections from active input lines to faulty output ports of the PDN [58]. Maze routing is an algorithm that uses a variant of the conventional face routing proposed for wireless adhoc networks, which randomly allocates output ports for flits whose productive ports are faulty [59, 60]. Routing is performed

using information contained in the flit header, which is updated as the flit hops out of every router. Although maze routing promises 100% fault coverage and guaranteed packet delivery on various topologies and deflection router architectures, majority of the flits are routed through non-minimal paths. The flits also require wider links to transport the extra bits in the flit header.

Maze routing adopts the golden and silver token mechanisms used in conventional CHIPPER and MinBD to resolve livelock while FaFNoC uses an age based hop counter in the flit header which is incremented at every hop [58, 59]. FTDR ensures livelock safety by prioritising older packets and using a converged routing table which ensures that packets advance towards their destinations deterministically [49]. From the study of previous literature, it is inferred that a precise fault model together with an efficient routing mechanism can improve the performance parameters of an NoC.

Table 2.2 Comparison of fault tolerant routing methods

| Proposed<br>Method | Fault<br>tolerant<br>routing<br>method  | Fault<br>coverage | Reconfiguration | Merits and<br>Limitations                                                                            |

|--------------------|-----------------------------------------|-------------------|-----------------|------------------------------------------------------------------------------------------------------|

| MD [19]            | Dynamic<br>XY                           | low               | Offline         | Disconnected network as the faults increase                                                          |

| ARIADNE [37]       | Adaptive routing table reconfigur ation | full              | Distributed     | Coarse grained<br>fault model,<br>low area<br>overhead, slow<br>reconfiguration,<br>poor scalability |

| Vicis [40]                | Static routing table reconfigur ation                                    | high     | Distributed | Improved coarse grained model BIST based, high area overhead, deadlock prone,                  |

|---------------------------|--------------------------------------------------------------------------|----------|-------------|------------------------------------------------------------------------------------------------|

| uDirec [41]               | Scoreboar<br>d updation<br>at<br>supervisor<br>y node                    | full     | Centralised | Fine grained fault model, high reconfiguration overhead                                        |

| TOSR [43]                 | Multiple<br>physical<br>networks<br>for<br>different<br>message<br>types | moderate | Distributed | Fast run-time reconfiguration, additional escape network required                              |

| Hermes [53]               | Routing table updation                                                   | moderate | Distributed | High area overhead                                                                             |

| NARCO<br>[54]             | OE turn<br>model<br>based<br>routing                                     | High     | Distributed | High overhead<br>for packet<br>redundancy                                                      |

| Immunet [38]              | Routing table                                                            | high     | Distributed | Coarse grained fault model, high overhead due to escape VC and three additional routing tables |

| LBDR,<br>uLBDR<br>[45,46] | Logic<br>Based                                                           | high     | Centralised | Low area overhead                                                                              |

| d2-LBDR<br>[44]         | Logic<br>Based                                                           | moderate | Centralised       | Low area overhead                                                                                                                           |

|-------------------------|--------------------------------------------------------------------------|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| FTDR,<br>FTDR-H<br>[49] | Deflection<br>routing<br>with<br>routing<br>table<br>updation            | High     | Fully distributed | Fast reconfiguration, handles transient and permanent faults, high flit prioritisation overhead.                                            |

| FoN [57]                | Deflection<br>routing<br>with<br>neighbor<br>fault<br>informatio<br>n    | Full     | Fully distributed | Fast reconfiguration, low throughput and high hop count                                                                                     |

| FaFNoC<br>[58]          | Deflection<br>routing by<br>disabling<br>faulty<br>links                 | Full     | Fully distributed | Low router area,<br>Less energy<br>efficient due to<br>high deflection<br>rate, high wiring<br>overhead due to<br>age based hop<br>counter. |

| Maze<br>routing [59]    | Deflection<br>routing<br>with<br>additional<br>header<br>informatio<br>n | Full     | Fully distributed | Guaranteed delivery, no reconfiguration overhead, non-minimal routing leads to higher latency, high wiring overhead.                        |

From the comparison of various fault tolerant routing techniques given in Table 2.2, it is observed that majority of the fault tolerant methods for permanent faults have been proposed for buffered VCR based NoCs. Reliability issues related to adaptive deflection router based NoCs needs to be addressed through extensive research. Routing techniques that deliver graceful performance even at high fault rates by exploring minimal fault-free paths are to be devised.

## 2.5 Thermal aware routing methods

Thermal distribution within a chip is an important factor for the long-term reliability of the chip. Thermal hotspots in certain areas of the chip cause uneven wear and tear leading to reduction in average lifetime of the chip. One reason for hotspot formation is due to high power consuming applications running on processor cores. Efficient application mapping techniques are one way of achieving an even thermal profile in the chip [61,62].

Another important aspect is the uneven distribution of NoC traffic due to poor load balancing capability of the routing methods which deliver high performance. In such NoCs, certain areas tend to be more congested than the rest due to concentration of traffic, creating an uneven thermal profile. Many papers related to thermal aware routing techniques were proposed in recent years. In input buffered routers, Regional Congestion Awareness (RCA) method uses congestion information of a region to improve load balancing capability of the network [63]. Global Congestion Awareness (GCA) and Global Load Balancing (GLB) are also similar approaches where information on global congestion is the metric used for load balancing [64, 65]. In the Free

Buffer Priority (FBP) scheme, the count of free input buffers in downstream routers is taken as a measure for adaptive selection of output ports [4]. In Buffer Occupancy Factor based Adaptive Router (BOFAR), the history of buffer occupancy time of flits decides congestion in a router [66].