# ACCELERATING TWO DIMENSIONAL FFT AND CONVOLUTIONAL NEURAL NETWORKS ON FPGA

A THESIS

submitted by

## KALA S

for the award of the degree

of

### DOCTOR OF PHILOSOPHY

in the Faculty of Engineering

# **DIVISION OF ELECTRONICS ENGINEERING,**

# SCHOOL OF ENGINEERING COCHIN UNIVERSITY OF SCIENCE AND TECHNOLOGY

January 2020

Copyright by Kala S 2020 All rights reserved

C

## THESIS CERTIFICATE

This is to certify that the thesis titled ACCELERATING TWO DIMENSIONAL FFT AND CONVOLUTIONAL NEURAL NETWORKS ON FPGA, submitted by Kala S., to Cochin University of Science And Technology, for the award of the degree of Doctor of Philosophy, is a bonafide record of research work done by her under my supervision and guidance at Division of Electronics Engineering, School of Engineering, Cochin University of Science And Technology. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

I further certify that the corrections and modifications suggested by the audience during the pre-synopsis seminar and recommended by the Doctoral Committee of Ms. Kala S are incorporated in the thesis.

**Dr. Babita Roslind Jose** Research Guide Associate Professor Division of Electronics Engineering, School of Engineering CUSAT, 682 022

Place: Kalamassery

Date: 15<sup>th</sup> January 2020

To Nalesh for his endless love and support...

# DECLARATION

I hereby declare that the work presented in the thesis entitled ACCELERATING TWO DIMENSIONAL FFT AND CONVOLUTIONAL NEURAL NETWORKS ON FPGA is based on the original research work carried out by me under the supervision and guidance of **Dr. Babita Roslind Jose**, Associate Professor, for the award of degree of Doctor of Philosophy with Cochin University of Science and Technology. I further declare that the contents of this thesis, in full or in parts, have not been submitted to any other University or Institute for the award of any degree or diploma.

Kochi - 682 022 Date: 15/01/2020

Kala S

### ACKNOWLEDGEMENTS

I am indebted to many people for their support during my life at CUSAT. First and foremost I would like to thank my supervisor Dr. Babita Roslind Jose for her guidance and support throughout the research period. I thank her for giving me the opportunity to work under her guidance in Division of Electronics. She was so approachable that her friendly attitude made it very interesting to work in the lab.

I express my deepest gratitude to Prof. Jimson Mathew, IIT Patna, for his guidance and motivation throughout my research period. He was the one who has introduced me to the world of research even before I join for MS(Engg) at IISc Bangalore. I thank him for trusting me and providing me all kind of supports for my research work. Without his encouragement and persistent help, this thesis would not have been possible. He was very instrumental in helping me while writing research papers and project proposals. Long discussions with him have given me a clear direction to go on. No words are sufficient to thank Prof. Jimson.

I am thankful to Dr. Shahana T.K., Head, Division of Electronics for providing me with all the academic and administrative support during my course of PhD. I also thank Prof. M.R.R. Panicker (former Principal, SOE), for all administrative supports that he has given to me without any hesitation during his tenure as a Principal. I am also grateful to Dr. Deepa Sankar and Dr. Rekha K. James for their valuable suggestions during the half-yearly presentations. I also thank Dr. Binu Paul and Dr. Mridula S for their timely help during my research period.

I would like to thank all research scholars in the department for creating an enthusiastic and dynamic environment. I especially thank my ex-lab mate Bijitha for being my good friend and critique. Our discussions in the lab range from computer vision to movies, food and politics. I thank Chitra and Chandny for giving me a good companionship during my life at CUSAT. I am also thankful to Debdeep Paul (Department of Electrical Engineering, IIT Patna) for helping me in my research with GPU simulations. I thank staff members of Audit section (Administration), SOE A-section (especially Mrs. Azra) and B-section for their co-operation in the administrative matters.

This work was in part funded by Kerala State Council for Science, Technology and Environment (KSCSTE) through Back-to-Lab (BLP) research fellowship under Woman Scientists Division (WSD). I am grateful to Dr. K.R. Lekha, Head of WSD, for her support and guidance in completion of this work. I would like to thank Prof. Deepak Mishra, Indian Institute of Space Science And Technology (IIST Trivandrum), for his valuable comments and guidance in completion of the KSCSTE project. I am extremely grateful to Prof.Mishra for the arrangements that he has provided for one week, during my visit to Virtual Reality Lab, IIST.

I am thankful to organizers of  $32^{nd}$  IEEE International Conference on VLSI Design &  $18^{th}$  Int'l Conference on Embedded Systems (VLSID), New Delhi, 2019, for providing me with the fellowship for attending and presenting my research paper. I also thank organizers of *VLSID* 2020, Bengaluru, for providing fellowship for presenting a poster at *Student Research Forum (Best SRF-Runner Up)*. I also thank Council of Scientific & Industrial Research (CSIR) for providing the travel grant for attending and presenting a paper in  $32^{nd}$  IEEE International System-On-Chip Conference (SOCC) 2019, at Singapore.

I thank my parents and sisters for supporting me throughout my life. I owe everything to my father for what I have achieved so far. I also thank my sisters' kids, (Hari, Mukundan, Harshan and Darshan) for entertaining my son Gautham whenever I was busy. My son, Gautham was born during the initial stage of my research. I am deeply indebted to my mother who has taken care of my son when both his father and mother were away for research work.

Thank you Nalesh for being with me always!

His love, care and support has really helped me in getting through this journey. Without his support and help I would not have joined for PhD. Nalesh could tactfully manage Gautham during my busy schedule of paper submission deadlines and conference travels.

This doctoral thesis is dedicated to Nalesh and Gautham.

Kala S. 15<sup>th</sup> January, 2020

### ABSTRACT

Signal processing domain has seen tremendous growth in research and applications over the past few decades. Digital Signal Processing (DSP) algorithms are widely used in image and video processing systems. These systems find applications in the field of multimedia, digital TV, radio, biomedical imaging, weather forecasting and gaming. With the increased capacity of transistors in a chip, realization of many of these applications is possible. Digital image processing is a field of DSP where digital images are processed by means of digital computers. Most of the steps in digital image processing like image analysis, image reconstruction, image enhancement and compression can be performed using Fast Fourier Transform (FFT) algorithm. Evolution of deep learning techniques enabled implementation of most of the image processing applications with high performance and accuracy. Most popular deep learning technique used for image classification and detection task is Convolutional Neural Network (CNN), which is a variant of deep neural network. There exist several hardware and software solutions for implementing these algorithms. Hardware implementations provide better performance per watt and are more suited for real-time embedded applications compared to software implementations. This thesis focus on hardware acceleration of two dimensional FFT and Convolutional Neural Networks for image processing systems.

In the first part of thesis, a two dimensional (2D) FFT architecture for image restoration and reconstruction is presented. A 2D FFT architecture using cascade of two radix- $4^3$  FFTs based on a parallel unrolled radix-4 butterfly unit is proposed in this work. A  $64 \times 64$  point 2D FFT architecture based on radix- $4^3$  algorithm using a parallel unrolled radix- $4^3$  FFT has been presented in this work. Radix- $4^3$  architecture in this work is a memory optimized parallel architecture which computes 64 point FFT, with least execution time. Row-column decomposition of two radix- $4^3$  blocks is used to compute a 2D FFT. Proposed architecture has been implemented in UMC 65nm 1P10M CMOS technology with a maximum clock frequency of 312.5 MHz and area of  $1.22mm^2$ . The architecture is also implemented in Xilinx Virtex-7 FPGA and the results are compared with state -of-art implementations. Second part of this thesis is focused on an efficient hardware accelerator for Convolutional Neural Networks (CNNs), which are widely used in image classification tasks. Recent researches have shown the effectiveness of FPGA as a hardware accelerator for CNNs which can deliver high performance at low power budgets. Majority of computations in CNNs involve 2D convolution. Winograd minimal filtering based algorithm is the most efficient technique for calculating convolution for smaller filter sizes. CNNs also consist of fully connected layers which are computed using General Element-wise Matrix Multiplication (GEMM). In the second work, an exploration of various algorithms for computing convolution layers in CNN is performed and complexity of these algorithms are compared. A unified architecture named UniWiG is proposed, where both Winograd based convolution and GEMM can be accelerated using the same set of processing elements. This approach leads to efficient utilization of FPGA hardware resources while computing all layers in CNN. We have mapped popular CNN models like AlexNet, VGG-16 and ResNet-18 onto the proposed accelerator and the measured performance compares favorably with other state-of-art implementations.

KEYWORDS: Digital Signal Processing; Deep Learning; Fast Fourier Transform; FPGA; CNN; Hardware acceleration; Performance.

# **TABLE OF CONTENTS**

| AC | CKNO | OWLEDGEMENTS                                             | i    |

|----|------|----------------------------------------------------------|------|

| Ał | BSTR | ACT                                                      | iii  |

| LI | ST O | F TABLES                                                 | X    |

| LI | ST O | F FIGURES                                                | xii  |

| AC | CRON | NYMS                                                     | xiii |

| N  | OTAT | ION                                                      | XV   |

| 1  | Intr | oduction                                                 | 1    |

|    | 1.1  | Motivation, Objective and Scope                          | 2    |

|    | 1.2  | Choosing a Solution                                      | 4    |

|    | 1.3  | Overview of Fast Fourier Transforms                      | 5    |

|    | 1.4  | Overview of Convolutional Neural Networks                | 6    |

|    | 1.5  | Contribution of the Thesis                               | 8    |

|    | 1.6  | Organization of the Thesis                               | 11   |

| 2  | Bac  | kground and Related Works                                | 13   |

|    | 2.1  | FFT Algorithms and Architectures                         | 13   |

|    |      | 2.1.1 Radix-2 Cooley-Tukey FFT                           | 14   |

|    |      | 2.1.2 Radix-4 FFT                                        | 15   |

|    |      | 2.1.3 2D FFT                                             | 16   |

|    | 2.2  | Convolutional Neural Networks                            | 19   |

| 3  | Rad  | ix-4 <sup>3</sup> based Two Dimensional FFT Architecture | 31   |

|   | 3.1 | Propos   | ed 2D FFT Architecture and Data Reordering                  | 32 |

|---|-----|----------|-------------------------------------------------------------|----|

|   |     | 3.1.1    | R4 <sup>3</sup> Algorithm                                   | 32 |

|   |     | 3.1.2    | $\mathbf{R4}^3$ Architecture                                | 34 |

|   |     | 3.1.3    | Data Scheduling in Proposed Architecture                    | 39 |

|   |     | 3.1.4    | 2D FFT Architecture                                         | 40 |

|   | 3.2 | Impler   | nentation Results and Analysis                              | 44 |

|   |     | 3.2.1    | Matlab Simulation                                           | 44 |

|   |     | 3.2.2    | ASIC Implementation                                         | 45 |

|   |     | 3.2.3    | FPGA Implementation                                         | 49 |

|   |     | 3.2.4    | Hardware Complexity Analysis                                | 50 |

|   | 3.3 | Summ     | ary of the Chapter                                          | 50 |

| 4 | Con | volutior | n Algorithms for CNN Implementation                         | 55 |

|   | 4.1 | Direct   | Convolution                                                 | 55 |

|   | 4.2 | FFT C    | onvolution                                                  | 58 |

|   | 4.3 | Winog    | rad minimal filtering                                       | 58 |

|   | 4.4 | Depthy   | wise Separable Convolution                                  | 61 |

|   | 4.5 | Analys   | sis of Convolution Schemes                                  | 61 |

|   | 4.6 | Trainir  | ng and Inference of CNN Models                              | 62 |

|   |     | 4.6.1    | CNN Models for Evaluation                                   | 63 |

|   |     | 4.6.2    | Implementation and Results                                  | 65 |

|   | 4.7 | Hardw    | are Architecture for AlexNet Model                          | 68 |

|   |     | 4.7.1    | FPGA Implementation Results                                 | 70 |

|   | 4.8 | Summ     | ary of the Chapter                                          | 71 |

| 5 | Uni | WiG: Uı  | nified Winograd-GEMM based CNN Architecture                 | 73 |

|   | 5.1 | Motiva   | ation                                                       | 73 |

|   |     | 5.1.1    | General Matrix Multiplication (GEMM)                        | 74 |

|   |     | 5.1.2    | Parallel Block Multiplication Scheme                        | 76 |

|   |     | 5.1.3    | Transforming Winograd Minimal Filtering Algorithm to GEMM   | 76 |

|   | 5.2 | 1        | ed Blocked Winograd Minimal Filtering Based Convolution Al- | 79 |

|   | 5.3 | -        | ed Unified Winograd-GEMM Accelerator Architecture           | 82 |

|      | 5.3.1          | Block RAM Memory Requirement          |

|------|----------------|---------------------------------------|

|      | 5.3.2          | Performance Model                     |

|      | 5.3.3          | Other Layers of CNN                   |

| 5.4  | Implei         | mentation and Results                 |

|      | 5.4.1          | Comparison with Baseline Architecture |

| 5.5  | Summ           | ary of the Chapter                    |

| 6 Pe | rformand       | ce Analysis of CNN Models on UniWiG   |

| 6.1  | Fixed          | point Implementation of UniWiG        |

|      | 6.1.1          | Batch Processing                      |

|      | 6.1.2          | Fixing the Winograd Tile Size         |

|      | 6.1.3          | Hardware Resource Utilization         |

|      | 6.1.4          | Performance Model Accuracy            |

| 6.2  | Compa          | arison with Existing Accelerators     |

| 6.3  | Summ           | ary of the Chapter                    |

| 7 Co | nclusion       | s and Future Work                     |

| 7.1  | Summ           | ary of the Thesis                     |

| A W  | NOGRA          | AD MINIMAL FILTERING COEFFICIENTS     |

| A.1  | $F(2 \times$   | $(2, 3 \times 3)$                     |

| A.2  | $2 F(3 \times$ | $3, 2 \times 2)$                      |

| A.3  | $F(3 \times$   | $(3, 3 \times 3)$                     |

| A.4  | $F(4 \times$   | $4, 3 \times 3)$                      |

| A.:  | 5 $F(6 \times$ | $6, 3 \times 3)$                      |

| REFE | RENCE          | 8                                     |

| PUBL | ICATIO         | NS BASED ON THESIS                    |

|      |                |                                       |

|      |                |                                       |

# LIST OF TABLES

| 1.1 | CONV Layers of Various CNN Models                                                    | 9  |

|-----|--------------------------------------------------------------------------------------|----|

| 2.1 | Various Approaches in CNN Accelerators                                               | 29 |

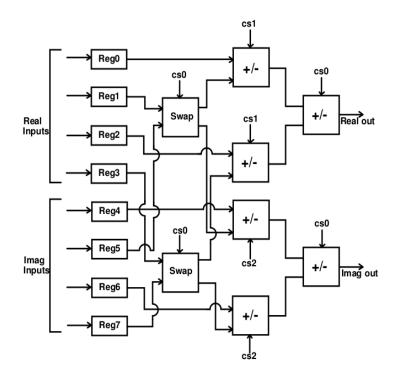

| 3.1 | Control Signals in Radix-4 Unit                                                      | 37 |

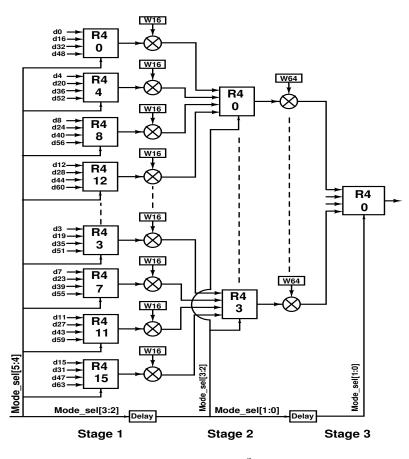

| 3.2 | Mode Selection in Different Stages of $R4^3$ Block                                   | 38 |

| 3.3 | ASIC Synthesis Results of $64 \times 64$ FFT $\ldots$                                | 48 |

| 3.4 | Comparison of Computation Time                                                       | 48 |

| 3.5 | FPGA Implementation Results of $64 \times 64$ FFT $\ldots$                           | 49 |

| 3.6 | Resource Utilization of $64 \times 64$ FFT                                           | 49 |

| 3.7 | Comparison of FFT Architectures                                                      | 52 |

| 3.8 | Hardware Complexity of various 1D FFT Architectures                                  | 53 |

| 4.1 | Hardware Complexity of Winograd Algorithm                                            | 59 |

| 4.2 | Design parameters for convolution                                                    | 61 |

| 4.3 | AlexNet Layer Configuration                                                          | 63 |

| 4.4 | VGG network models                                                                   | 64 |

| 4.5 | Resource Utilization                                                                 | 71 |

| 4.6 | Performance Comparison                                                               | 71 |

| 5.1 | Performance comparison with baseline architecture in Shen et al. (2018)              | 91 |

| 5.2 | Comparison of FPGA resources with baseline architecture in Shen <i>et al.</i> (2018) | 92 |

| 6.1 | AlexNet CONV parameters for various tile sizes                                       | 94 |

| 6.2 | Estimated BRAM for various tiles in AlexNet                                          | 95 |

| 6.3 | Estimated BRAM for Various Tiles in VGG-16                                           | 96 |

| 6.4 | ResNet-18 parameters for various tiles                                               | 97 |

| 6.5 | Convolution Schemes for various layers in ResNet-18                                  | 97 |

| 6.6 | BRAM for various tiles in ResNet-18                                                  | 98 |

| 6.7 | Hardware Resource Utilization                                                        | 99 |

| 6.8  | Performance Model Accuracy for CONV layers in AlexNet | 100 |

|------|-------------------------------------------------------|-----|

| 6.9  | Comparison of AlexNet CNN Implementations             | 101 |

| 6.10 | Comparison of VGG CNN Implementations                 | 102 |

| 6.11 | Comparison of ResNet models                           | 103 |

# LIST OF FIGURES

| 1.1  | Digital Image Processing Gonzalez and Woods (2008)                                                                                             | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Convolutional Neural Network Model                                                                                                             | 7  |

| 2.1  | Butterfly diagram of Radix-2 DIF FFT                                                                                                           | 14 |

| 2.2  | Radix-4 DIF FFT Butterfly                                                                                                                      | 15 |

| 2.3  | Neuron in the brain                                                                                                                            | 20 |

| 2.4  | Typical Neural Network                                                                                                                         | 20 |

| 2.5  | Convolution Operation                                                                                                                          | 23 |

| 2.6  | Hardware Utilization for AlexNet implementation                                                                                                | 25 |

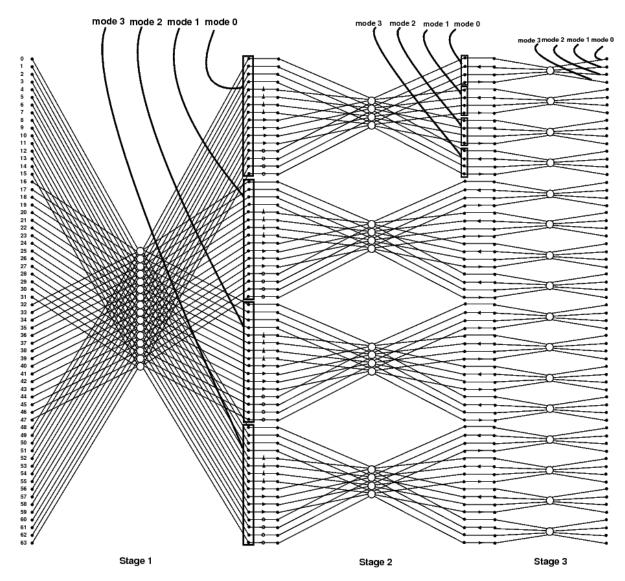

| 3.1  | Signal Flow Graph of $\mathbb{R}4^3$ algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                              | 35 |

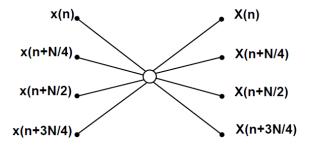

| 3.2  | Nodal representation of radix-4 butterfly                                                                                                      | 35 |

| 3.3  | Radix-4 Butterfly Unit                                                                                                                         | 36 |

| 3.4  | Radix-4 <sup>3</sup> block                                                                                                                     | 37 |

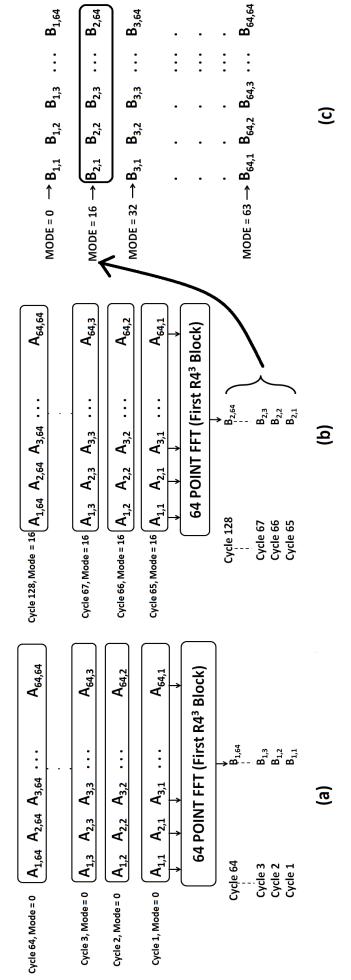

| 3.5  | Data Scheduling in First Radix- $4^3$ Block (a) Output when $Mode = 0$<br>(b) Output when $Mode = 16$ (c) Output for $Mode = 0$ to $Mode = 63$ | 41 |

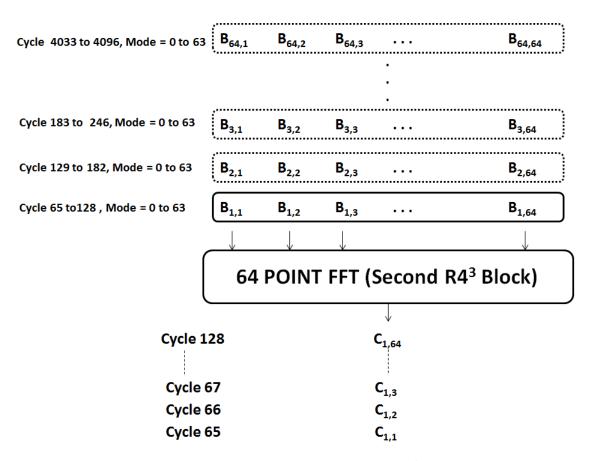

| 3.6  | Data Scheduling in Second Radix-4 <sup>3</sup> Block                                                                                           | 42 |

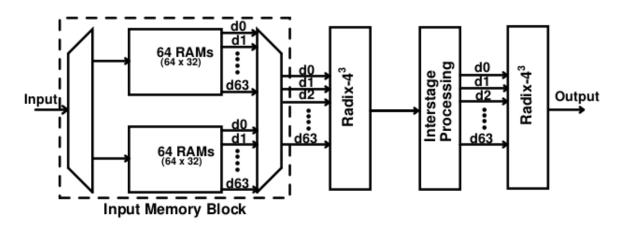

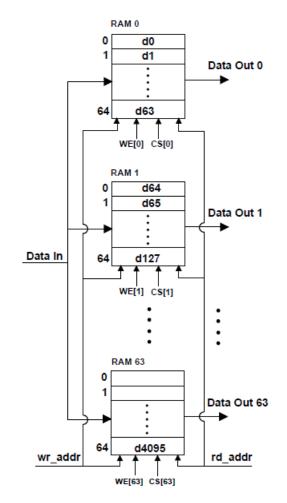

| 3.7  | Proposed 2D FFT Architecture using R4 <sup>3</sup> blocks                                                                                      | 42 |

| 3.8  | Input Memory                                                                                                                                   | 43 |

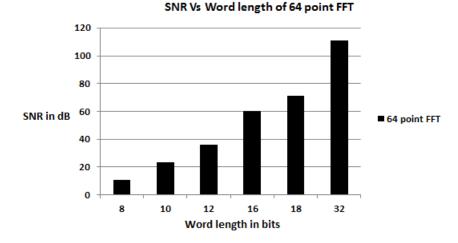

| 3.9  | SNR Vs Word length for 64 point FFT using Radix- $4^3$ Algorithm .                                                                             | 45 |

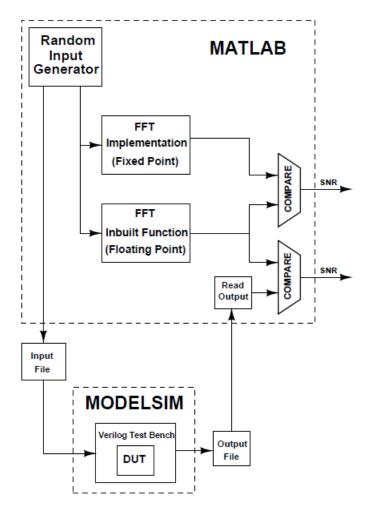

| 3.10 | Verification                                                                                                                                   | 47 |

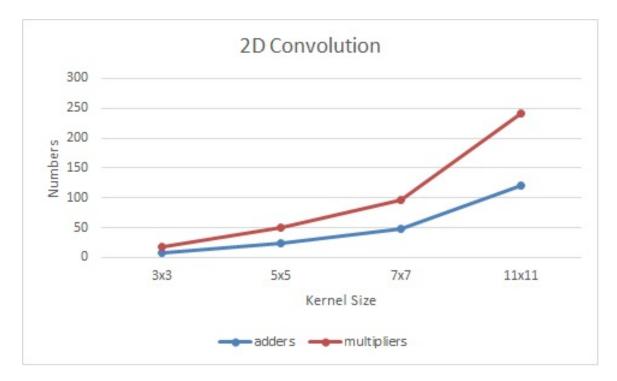

| 4.1  | Two dimensional convolution                                                                                                                    | 56 |

| 4.2  | Complexity analysis of 2D convolution                                                                                                          | 56 |

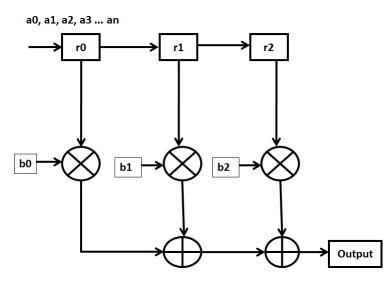

| 4.3  | Architecture of 1D Convolution                                                                                                                 | 57 |

| 4.4  | Architecture of 2D Convolution                                                                                                                 | 57 |

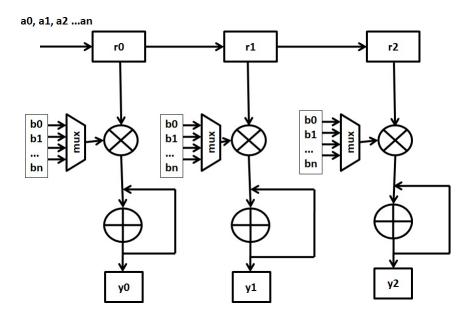

| 4.5  | FFT based convolution                                                                                                                          | 58 |

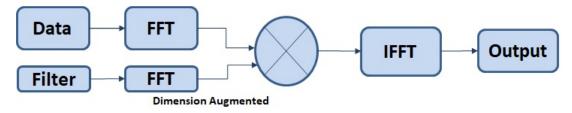

| 4.6  | Execution time for various convolution schemes                                                                                                 | 62 |

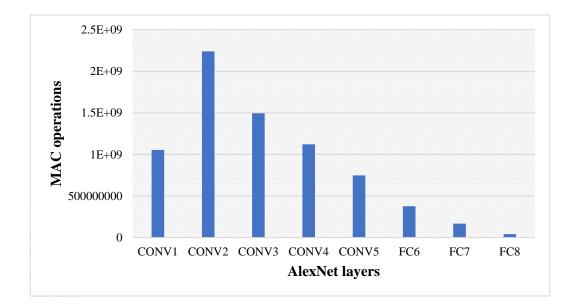

| 4.7  | MAC Operations in AlexNet                                                                                                                      | 64 |

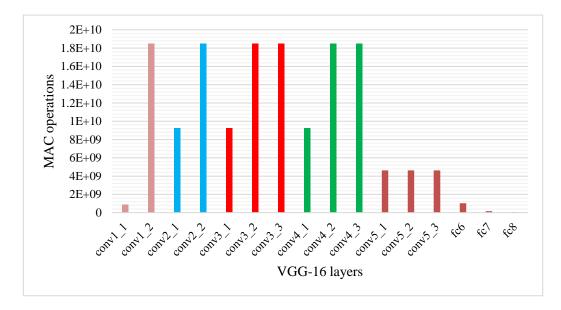

| 4.8  | MAC Operations in VGG-16                          | 65 |

|------|---------------------------------------------------|----|

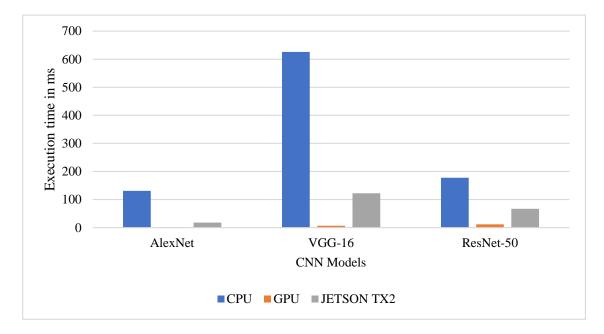

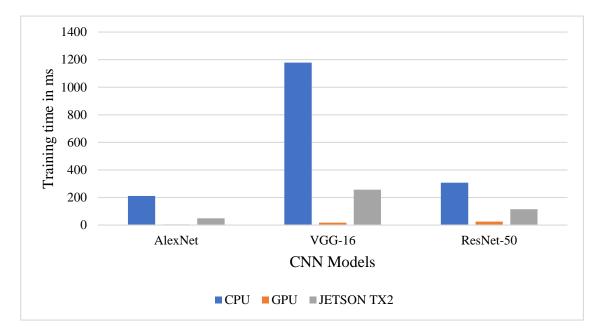

| 4.9  | Comparison of feed forward simulations            | 66 |

| 4.10 | Comparison of training periods                    | 67 |

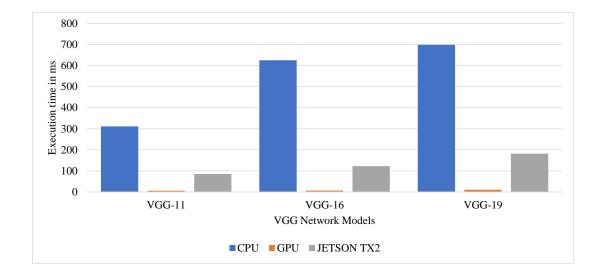

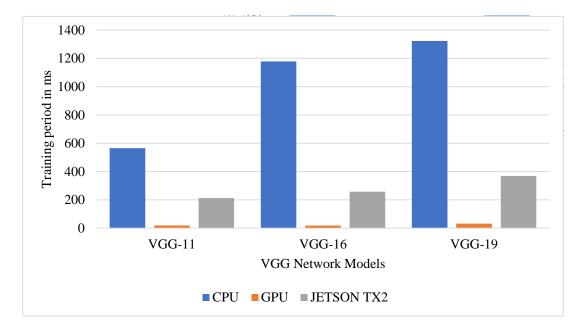

| 4.11 | Comparison of inference time of VGG networks      | 67 |

| 4.12 | Comparison of training periods of VGG networks    | 68 |

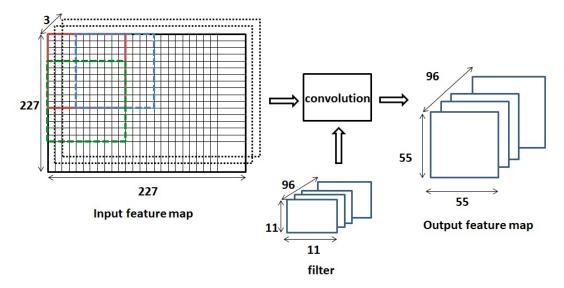

| 4.13 | CONV1 layer of AlexNet                            | 69 |

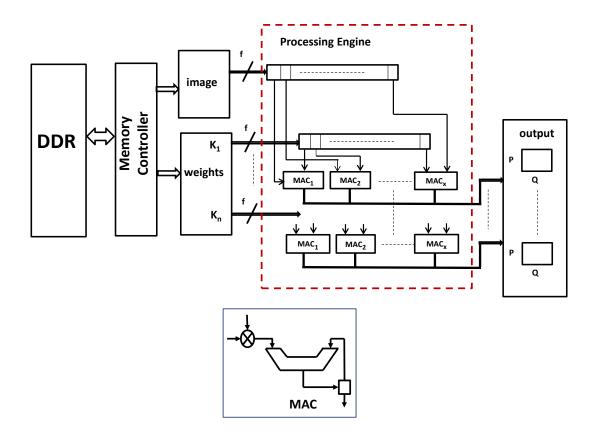

| 4.14 | Proposed Architecture                             | 70 |

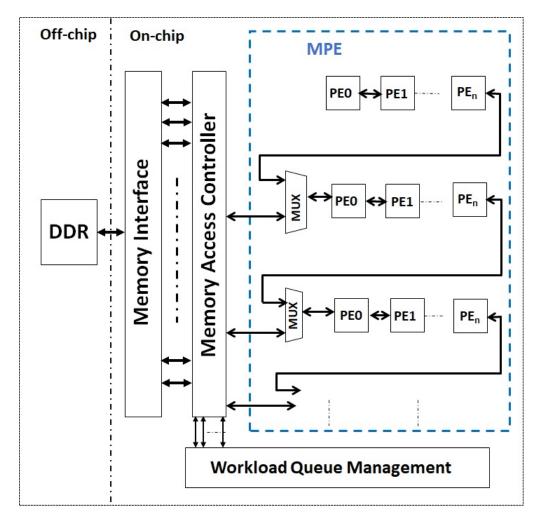

| 5.1  | GEMM Accelerator in Shen <i>et al.</i> (2018)     | 75 |

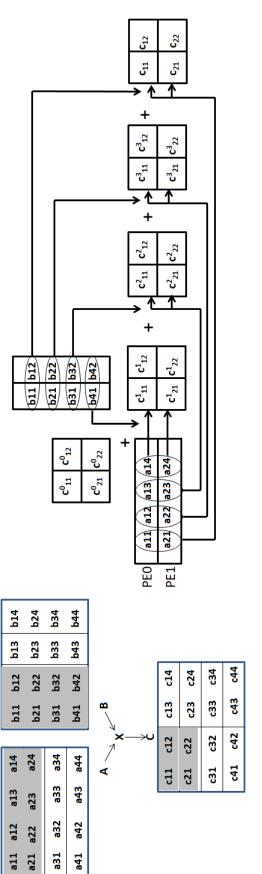

| 5.2  | Parallel Block Matrix Multiplication Scheme       | 77 |

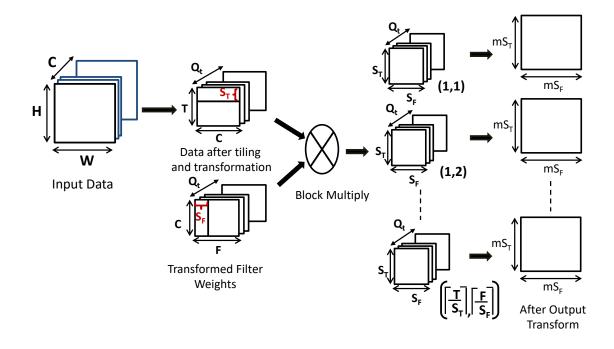

| 5.3  | Blocked Winograd Minimal Filtering Algorithm      | 82 |

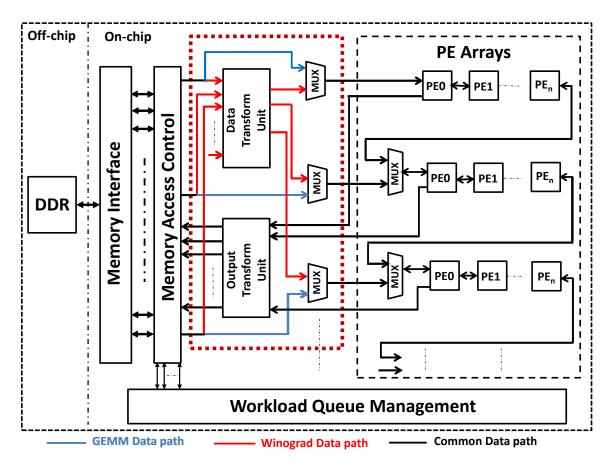

| 5.4  | Proposed Unified Winograd-GEMM Architecture       | 83 |

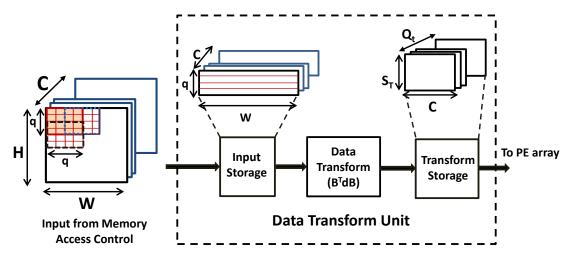

| 5.5  | Data Transform Unit                               | 84 |

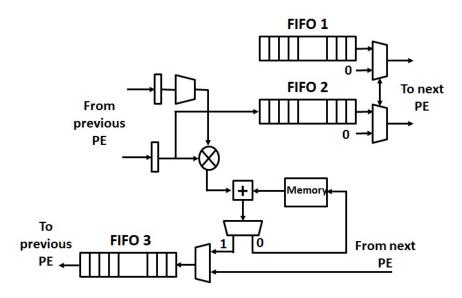

| 5.6  | Processing Element (PE) Shen et al. (2018)        | 85 |

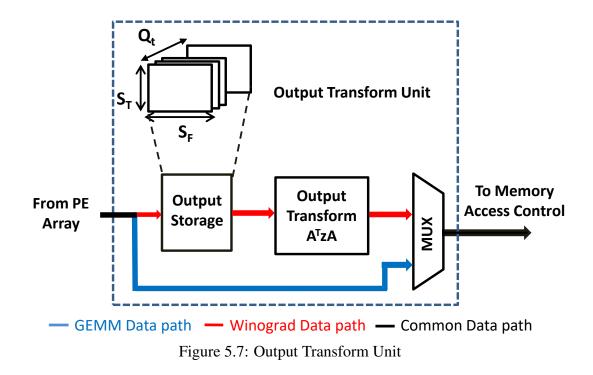

| 5.7  | Output Transform Unit                             | 87 |

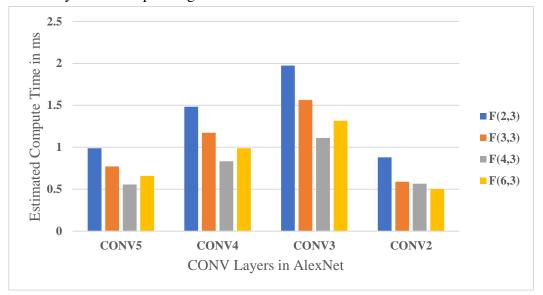

| 6.1  | Estimated compute time for CONV Layers in AlexNet | 95 |

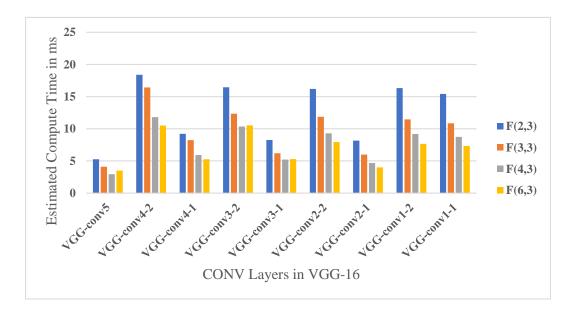

| 6.2  | Estimated compute time for CONV Layers in VGG-16  | 96 |

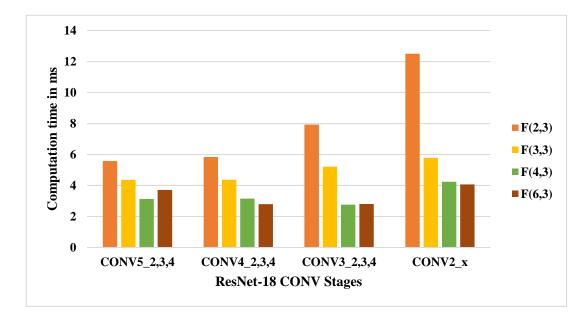

| 6.3  | Compute time for ResNet-18 CONV layers            | 98 |

|      |                                                   |    |

# ACRONYMS

| 1D     | One Dimensional                                   |

|--------|---------------------------------------------------|

| 2D     | Two Dimensional                                   |

| ASIC   | Application Specific Integrated Circuit           |

| BRAM   | Block Random Access Memory                        |

| CMOS   | Complemenatry Metal Oxide Semiconductor           |

| CNN    | Convolutional Neural Network                      |

| DDR    | Double Data Rate                                  |

| DFT    | Discrete Fourier Transform                        |

| DIF    | Decimation In Frequency                           |

| DIP    | Digital Image Processing                          |

| DIT    | Decimation In Time                                |

| DNN    | Deep Neural Network                               |

| DSP    | Digital Signal Processing                         |

| FC     | Fully Connected                                   |

| FFT    | Fast Fourier Transform                            |

| FPGA   | Field Programmable Gate Array                     |

| GEMM   | General Element-wise Matrix Multiplication        |

| GFLOPS | Giga Floating Point Operations Per Second         |

| GOPS   | Giga Operations Per Second                        |

| GPP    | General Purpose Processor                         |

| GPU    | Graphics Processing Unit                          |

| IFFT   | Inverse Fast Fourier Transform                    |

| ILSVRC | ImageNet Large Scale Visual Recognition Challenge |

| LUT    | Look Up Table                                     |

| MAC    | Multiply And Accumulate                           |

| MDC    | Multi-path Delay Commutator                       |

| PE     | Processing Element                                |

| RAM    | Random Access Memory                              |

| ROM    | Read Only Memory             |

|--------|------------------------------|

| RTL    | Register Transfer Logic      |

| SDC    | Single-path Delay Commutator |

| SDF    | Single-path Delay Feedback   |

| SFG    | Signal Flow Graph            |

| SRAM   | Static Random Access Memory  |

| SNR    | Signal to Noise Ratio        |

| TF     | Twiddle Factor               |

| UniWiG | Unified Winograd GEMM        |

| VLSI   | Very Large Scale Integration |

# NOTATIONS

| $mm^2$           | Area in millimeter square |

|------------------|---------------------------|

| $\mu \mathbf{s}$ | Time in micro seconds     |

| MHz              | Frequency in Mega Hertz   |

| V                | Votage in Volts           |

| mW               | Power in milliwatts       |

| J                | Energy in Joules          |

### **CHAPTER 1**

#### Introduction

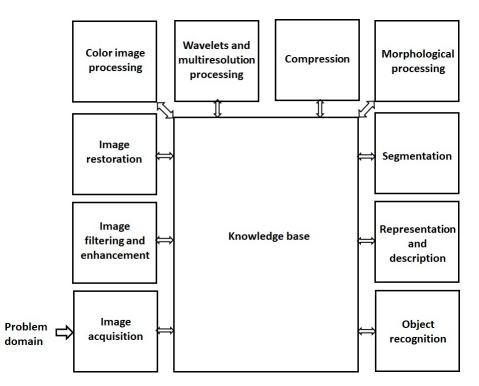

Rapid advancements in science and technology has paved path for researches in developing machines which have faster processing capabilities than human brain. Image processing and machine learning are currently active areas of research due to their wide range of applications like surveillance, safety, medical field, games and entertainment and so on. Digital Image Processing (DIP) refers to processing of digital images using digital computers as described in Gonzalez and Woods (2008). Fundamental steps in digital image processing is explained in Fig. 1.1 Gonzalez and Woods (2008). Some of these processes are acquisition, image enhancement, image restoration and reconstruction, color image processing, wavelets and multi-resolution processing, compression, morphological processing, segmentation, representation, object detection and recognition. An image is captured by the sensor (or a camera) in image acquisition stage. In image enhancement, an image is manipulated to get a suitable result compared to the actual image, depending on the application. Image restoration and reconstruction refers to improvements in the appearance of an image. In color processing, the color of an image is used to extract certain features. Wavelets and compression techniques are used to reduce the size of an image. In morphological processing, feature extraction for representation of shape is performed. Image segmentation is one of the difficult operations in DIP, where the objects are separated from the background of the image. Representation and description can be either of two types, namely, boundary representation or region representation. Recognition refers to labeling the image based on the descriptors. Interaction between these modules is controlled by 'Knowledge Base'. Most of these processes can be performed using Digital Signal Processing (DSP) algorithms like Discrete Fourier Transform (DFT), Discrete Cosine Transform (DCT) and machine learning algorithms.

Image reconstruction is computationally demanding operation and a standard CPU or computer is not an efficient solution for performing real-time image reconstruction. A digital image processing system consists of sensors, specialized image processing

Figure 1.1: Digital Image Processing Gonzalez and Woods (2008)

hardware and software, computer, storage devices and displays. Frame rate and resolution of the sensor and reconstruction time are important factors which affect the performance of the image processing system. For performing certain signal processing operations where speed or performance is a critical parameter, hardware accelerators play key role. This thesis describes about hardware accelerators used in DIP systems for improving the performance. In this chapter, motivation for this research, along-with the objectives and scope of this thesis are presented.

### **1.1** Motivation, Objective and Scope

Researches in digital image processing has witnessed tremendous advances in the past few years which has become an interesting area for researchers all over the globe. Digital signal processing algorithms are the key components in majority of image processing applications. Hence efficient implementations of these algorithms have become a vital part in realizing these applications in a real-time environment. Fast Fourier Transform (FFT) and Convolutional Neural Networks (CNNs) are the two key techniques used in many phases in digital image processing systems. There exist several hardware and software solutions for FFT implementation. Hardware implementations provide better performance per watt and are more suited for real time embedded applications. Since FFT is a computationally intensive operation, realizing an *output reordered FFT* in hardware has become a challenging task. Most of the hardware accelerators for FFT do not perform output reordering, considering that the succeeding tasks or modules will take care of the reordering issues. Otherwise, in addition to FFT module, another reordering block will be present, which increases the hardware cost. The main objective of first part of this thesis is to develop a two dimensional (2D) FFT architecture which can perform data reordering without extra hardware cost. Reduction of intermediate memory, thereby reducing the latency and improving the FFT computation time and performance is also aimed in this thesis.

In the second part of this thesis, a high-performance Convolutional Neural Network (CNN) accelerator for image classification and segmentation is presented. Computational complexity of CNNs come from convolutional layers, which account for 90% of the computations in CNN Huimin Li et al. (2016). Deployment of CNNs on embedded systems with lower processing power and smaller power budget is a challenging task. Recent researches have shown the effectiveness of Field Programmable Gate Arrays (FPGA) as a hardware accelerator for CNNs which can deliver high performance at low power budgets. Majority of computations in CNNs involve 2D convolution. Algorithms like conventional or direct convolution, FFT based convolution and Winograd minimal filtering are generally used for implementing convolutional layers Shen et al. (2018); Lavin and Gray (2016). Suitable algorithm should be selected for realizing various convolution layers of a model, based on input feature size and filter size. Winograd minimal filtering based algorithm Winograd (1980) is the most efficient technique for calculating convolution for smaller filter sizes Ahmad and Pasha (2019). CNNs also consist of fully connected layers which are computed using General Element-wise Matrix Multiplication (GEMM). Most of the researchers use dedicated processing elements for performing Winograd convolutions. The drawback here, is the need for separate processing elements to accelerate convolutional layers and fully connected layers, which result in severe under-utilization of resources.

Winograd algorithm is suited only for convolutional layers with small kernel sizes. In case of the CNN model AlexNet Krizhevsky *et al.* (2012), first convolutional layer needs direct convolution and other convolutional layers can be efficiently accelerated using Winograd convolution. If we can perform direct convolution, Winograd convolution and fully connected layer computation using the same compute resources, we can achieve significant savings in hardware. The main objective of the second part of this thesis is to develop an efficient hardware accelerator for CNNs, which are widely used in image classification tasks. This work presents a unified architecture named *Uni-WiG*, where both Winograd based convolution and GEMM can be accelerated using the same set of processing elements. This approach leads to efficient utilization of FPGA hardware resources while computing all layers in CNN.

#### **1.2** Choosing a Solution

Selection of a suitable platform for implementation is a challenging task. Several technology solutions are available for implementation of signal processing tasks. Digital Signal Processors (DSP) are suited for implementing signal processing tasks, but they give very less throughput. Similar is the case with General Purpose Processors (GPP). Their power consumption is also very high. Hence software solutions for DSP implementations are not very efficient. Graphics Processing Units (GPU) also consume high power and are rarely used for embedded systems. Application Specific Integrated Circuit (ASIC) solutions give better performance with limited flexibility. Field Programmable Gate Arrays (FPGA) are flexible and gives high performance, with decent power consumption. FFT processors in the first work are implemented both in ASIC and in FPGA for evaluating the performance.

CNN is the most commonly used algorithm for image classification. Although DNN and CNN algorithms have been in existence over a long period of time, practical application of these algorithms started recently only. These algorithms are massively compute intensive and training the network can take multiple days to complete. Only with the deployment of GPUs, significant improvement has been achieved in bringing down the training time so as to be used in real life applications.

Most of the operations in CNNs can be reduced to matrix multiplication operations which consist of significant amount of parallelism. GPUs provide a platform for easily parallelizing matrix multiplication operation and thus improve the performance of CNNs. However, GPU implementation of CNNs suffer from high power consumption which prevents its adoption in embedded applications Huimin Li *et al.* (2016). A dedicated hardware accelerator for CNN is required to achieve maximum performance at relatively lower power consumption. FPGA based implementations give significant performance improvement at acceptable power dissipation.

#### **1.3** Overview of Fast Fourier Transforms

Over the past few decades signal processing domain has seen explosive growth in research and applications. Discrete Fourier Transform (DFT) is one of the essential part in digital signal processing and communication systems. Fast Fourier Transforms (FFTs) are widely used in image/video processing, Cognitive Radio, speech processing and various biomedical applications. FFT is a faster technique to perform Discrete Fourier Transforms (DFT) Proakis and Manolakis (1996). Cooley-Tukey is the common algorithm to find FFT of a sequence, since it reduces the complexity from  $O(N^2)$  to  $O(Nlog_2N)$  as compared to DFT J.W.Cooley and J.W.Tukey. (1965). One dimensional Discrete Fourier Transform for x(n), an N point sequence, can be computed as in Equation (1.1) Proakis and Manolakis (1996)

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk} \quad k = 0, 1, 2, \dots N - 1$$

(1.1)

where  $W_N$ , the Twiddle Factor, denotes the  $N^{th}$  primitive root of unity, with its exponent evaluated to *modulo* N and is introduced by Equation (1.2).

$$W_N = e^{-2\pi i/N} \tag{1.2}$$

An N-point inverse DFT (IDFT) can be calculated as given in Equation 1.3.

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) W_N^{-nk} \quad n = 0, 1, 2, \dots N - 1$$

(1.3)

IDFT requires few more logic like division and conjugate operation apart from the logic applied in DFT. Conventional image reconstruction uses inverse Fast Fourier Transform techniques. Inverse FFT (IFFT) is directly computed from FFT, and hence separate

architecture for IFFT is not discussed in research papers.

Multidimensional Fourier Transforms find wide range of application in signal processing systems. Multidimensional FFTs frequently find applications in video and image processing like reconstruction, medical imaging, radar signal processing etc. Image reconstruction is a key component in signal processing applications like medical imaging, computer vision, face recognition etc. Reconstruction of images is an important operation in most of these applications and involves complex computations in real time. Two Dimensional (2D) FFTs which are used for reconstructing image from raw data is computationally intensive and needs efficient implementations for catering to real time applications. These applications require large memory sizes to support large size images. Therefore it is necessary to have an FFT architecture which optimizes the memory but supports various image sizes, and provides the required throughput. For hardware mapping of the architecture, a 2D FFT is split into one dimensional FFTs which are performed over rows and then columns, generally referred as row-column decomposition. Equation (1.4) gives a relation between the hardware architecture parameters and system performance Lenart (2008).

$$f \times T = 2N^2 \times f_{rate} \tag{1.4}$$

$$Area \propto T$$

where, f denotes system frequency, T gives throughput, N is the size of the FFT,  $f_{rate}$  is the frame rate and Area is the complexity of the architecture.

#### **1.4** Overview of Convolutional Neural Networks

Deep Neural Networks (DNN) have revolutionized a variety of applications in varying domains like autonomous vehicles, weather forecasting, cancer detection, surveillance, traffic management, pattern recognition, image classification and speech recognition. Convolutional Neural Network (CNN) is a variant of DNN, where computations are performed as convolutions. CNN is the state-of-art technique for many machine learning tasks in image and video processing domain. CNN is the most commonly used algorithm for image classification and recognition. Most of the layers in CNN are not

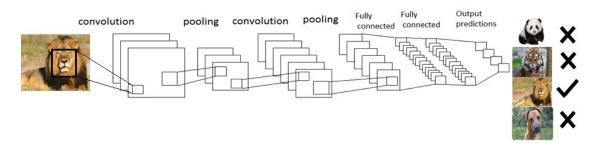

Figure 1.2: Convolutional Neural Network Model

fully connected layers as in other deep learning architectures. Instead, images are divided into tiles and convolution operation is performed to each tile with a filter (kernel) tile. The filter coefficients or weights are common for all tiles in a single image vector. Hence the number of weights for a convolution layer is considerably less than an equivalent fully connected layer. Typically CNNs consist of three main layers namely, convolutional layer (CONV) which performs feature extraction, max pooling (POOL) which is for sub sampling and fully connected (FC) layer for classification. A typical CNN is shown in Fig. 1.2.

Various CNN models were proposed from ImageNet Large-Scale Visual Recognition Challenge (ILSVRC) in the last few years, with varying number of CONV layers and filter sizes. Popular CNN models include AlexNet, which won ImageNet Challenge in 2012 Krizhevsky *et al.* (2012), Overfeat (ImageNet 2013) Sermanet *et al.* (2014), VGG Simonyan and Zisserman (2015) and GoogLeNet Szegedy *et al.* (2015) (ImageNet 2014) and ResNet (ImageNet 2015) He *et al.* (2016). AlexNet Krizhevsky *et al.* (2012), has five CONV layers and three FC layers. Overfeat Sermanet *et al.* (2014) also has five CONV and three FC layers, but with more number of filters. VGG has different models like VGG-11, VGG-13, VGG-16 and VGG-19, which has deeper layers Simonyan and Zisserman (2015). GoogleNet Szegedy *et al.* (2015) goes much more deeper, with 22 layers. ResNet He *et al.* (2016) has exceeded human level accuracy, with more than 34 layers.

Convolutions in a CNN are two dimensional (2D) operations where the input image is convolved with kernel, which is a multiply and accumulate (MAC) operation. One dimensional convolution which operates on two signals I(x) and f(x) is described as in (1.5).

$$f(x) * I(x) = \sum_{k=-\infty}^{+\infty} f(x)I(x-k)$$

(1.5)

A two dimensional (2D) convolution can be computed from one dimensional convolution as in (1.6).

$$f(x,y) * I(x,y) = \sum_{u=-\infty}^{+\infty} \sum_{v=-\infty}^{+\infty} f(u,v)I(x-u,k-v)$$

(1.6)

This is the generic mathematical formula for computing convolutions. Now consider an  $M \times N$  input image (I) and  $P \times Q$  kernel (F), which slides over the input image with a stride S to give  $R \times C$  output (O). In 2D convolution, each value of the input image is multiplied with each element of the convolution kernel and the outputs are summed together. Pseudo code for two dimensional convolution is given in Algorithm 1.

| Algorithm 1: Pseudo code for 2D Convolution                               |

|---------------------------------------------------------------------------|

| $M \times N$ is the input image size.                                     |

| $P \times Q$ is the kernel size.                                          |

| S is the stride of sliding window.                                        |

| $R \times C$ is the output image size.                                    |

| for $(r = 0; r < R; r + +)$                                               |

| for $(c = 0; c < C; c + +)$                                               |

| $O[r][c] + = \sum_{i=0}^{P-1} \sum_{j=0}^{Q-1} F[i][j] * I[r+S+i][c+S+j]$ |

In CNNs, there will be multiple channels of input and kernels, and the outputs from each channel are added up together to get the final result. A summary of CONV layers of various popular CNN models is given in Table 1.1.

#### **1.5** Contribution of the Thesis

Hardware acceleration of signal processing algorithms are on high demand for realtime embedded systems. The purpose of this work is to develop efficient hardware architecture for digital image processing systems. In the first part of thesis, an efficient two dimensional (2D) FFT architecture for image reconstruction, based on radix- $4^3$ algorithm has been presented. Here, a  $64 \times 64$  point 2D FFT architecture based on radix- $4^3$  algorithm using a parallel unrolled radix- $4^3$  FFT as the basic block has been proposed. Proposed radix- $4^3$  architecture is a memory optimized parallel architecture which computes 64 point FFT, with least execution time. Here we use row-column decomposition of two radix- $4^3$  blocks to compute a 2D FFT. Following are the key

|                | AlexNet                        | Overfeat                            | VGG-16                                   | GoogLenet                          | ResNet                  |

|----------------|--------------------------------|-------------------------------------|------------------------------------------|------------------------------------|-------------------------|

|                | Krizhevsky<br>et al.<br>(2012) | Sermanet<br><i>et al.</i><br>(2014) | Simonyan<br>and Zis-<br>serman<br>(2015) | Szegedy<br><i>et al.</i><br>(2015) | He <i>et al.</i> (2016) |

| $Feature_{in}$ | 224×224                        | 231×231                             | 224×224                                  | 224×224                            | 224×224                 |

| CONV<br>layers | 5                              | 5                                   | 13                                       | 57                                 | 53                      |

| Filters        | 11, 5, 3                       | 11, 5, 3                            | 3                                        | 1, 3, 5, 7                         | 1, 3, 7                 |

| Stride         | 4, 1                           | 4, 1                                | 1                                        | 1, 2                               | 1, 2                    |

| Parameters     | 2.3 M                          | 16 M                                | 14.7 M                                   | 6.0 M                              | 23.5 M                  |

| MAC            | 666 M                          | 2.67 G                              | 15.3 G                                   | 14.3 G                             | 3.86 G                  |

Table 1.1: CONV Layers of Various CNN Models

contributions of first part of the thesis.

- A novel architecture for computing two dimensional FFT based on radix-4<sup>3</sup> algorithm

- An efficient output reordering technique using the six-bit control signal

- Memory reduction within 1D FFT and optimizing the intermediate memory between two 1D FFTs from N<sup>2</sup> to N.

- ASIC and FPGA implementations of the proposed architecture were performed. Comparison of proposed work with the state-of-art implementations and show significant improvement in computation time and the comparable area in terms of slice look-up tables (LUTs).

Proposed architecture has been implemented in UMC 65nm 1P10M CMOS technology with a maximum clock frequency of 312.5 MHz and area of  $1.22mm^2$ . The architecture is also implemented in Xilinx Virtex-7 FPGA and the results are compared with state-of-art implementations.

In the second part of this thesis, various techniques for implementation of convolution layers and fully connected layers in CNNs were discussed. Training and inference of different CNN models on various platforms were discussed. Based on the analysis of algorithms and hardware availability, a high performance CNN accelerator based on Winograd minimal filtering and general matrix multiplication (GEMM) is presented. A unified, blocked Winograd-GEMM architecture for accelerating CNNs on FPGA has been proposed, where, CONV layers and FC layers can be implemented using efficient hardware utilization. An architecture, where both GEMM and Winograd filtering can be performed using the same processing element arrays has been presented. Block matrix multiplication scheme has been used for improving the efficiency and bandwidth. We propose a blocked version of Winograd minimal filtering algorithm for higher performance of the accelerator. Following are the key contributions of this work.

- Design space exploration of various algorithms for performing convolutions in CNN has been performed. Also, training and inference time of various layers in the feed forward network of AlexNet, VGG-16 and ResNet on platforms like GPP, GPU, server and Jetson TX2 board were performed.

- A unified architecture for performing general element-wise matrix multiplication (GEMM) as well as Winograd filtering algorithm using the same array of processing elements (PEs) has been proposed. Such a unified architecture gives the most efficient implementation for CONV layers irrespective of the filter sizes and also for FC layers. Winograd filtering is transformed to a GEMM operation as proposed in Lavin and Gray (2016) so that PEs for GEMM can be reused for Winograd algorithm.

- A novel algorithm is proposed, which transforms Winograd minimal filtering algorithm into blocked general element-wise matrix multiplication which targets optimal utilization of BRAMs and DDR bandwidth.

- An analytical model for estimating performance and BRAM usage has also been proposed, using which appropriate tile sizes for each layer can be identified, which can be used to optimize the tile size for a given convolution layer.

- The proposed architecture has been used to accelerate popular CNN models like AlexNet, VGG-16 and ResNet-18 models on Xilinx XC7VX690T FPGA. Comparison of various CNN implementations has been performed to show the efficiency of proposed accelerator.

To maximize the resource utilization, we have designed the architecture of the accelerator, a reusable one. Conventionally, CNNs like AlexNet, VGGNet etc follw a layer-by-layer sequential operation. A layer-by-layer computation flow of CNN has been designed in this work. Proposed architecture has been implemented on Xilinx XC7VX690T FPGA using both single precision floating point arithmetic and 16-bit fixed point arithmetic. Since various layers in a CNN are to be sequentially exectuted even in an end-to-end implementation, FPGA resources remain the same.

### **1.6** Organization of the Thesis

The main theme of this research work is to develop efficient architectures for high performance image processing applications, in a real-time scenario.

Chapter 2 covers various existing FFT algorithms and architectures in literature. Hardware complexity analysis of different architectures and output reordering techniques are also discussed in this chapter. Secondly, a survey of various CNN accelerators implemented using GPU, ASIC and FPGA are carried out and explored different CNN implementations. A study of CNN architectures based on different convolution algorithms has also been conducted.

Chapter 3 discusses radix- $4^3$  based two dimensional FFT architecture. Here, a 2D FFT architecture based on cascade of two unrolled parallel-pipelined radix- $4^3$  FFT has been discussed. A 64×64 point 2D FFT architecture is implemented in ASIC and FPGA and comparison has been performed with various existing 2D FFT architectures to show the effectiveness of our architecture.

In Chapter 4, an exploration of various convolution algorithms are performed. Merits and demerits of various convolution schemes for CNN are discussed in this chapter. Need for a unified Winograd-GEMM architecture is also briefly explained. In this chapter, training and inference of popular network models in CPU, GPU and Jetson TX2 platforms are also presented. An FPGA based architecture for accelerating AlexNet CNN model is also discussed in this chapter.

In Chapter 5, blocked version of Winograd minimal filtering algorithm is presented. Unified Winograd-GEMM architecture for accelerating CNNs on FPGA is proposed in this chapter. Blocking techniques for improving the performance are also discussed. An analytical model for estimating performance and BRAM usage has also been proposed, using which appropriate tile sizes for each layer can be identified. Floating point implementation of AlexNet model on FPGA is described here and compared with the existing architecture.

In Chapter 6, FPGA implementation details of proposed CNN architecture in fixed point arithmetic are explained and the results are discussed. Fixed point implementation of AlexNet, VGG-16 and ResNet-18 models are performed and the results are evaluated. Comparisons with state-of-art implementations are also done in this chapter.

Chapter 7 presents the conclusions and future directions of this research work.

# **CHAPTER 2**

# **Background and Related Works**

In this chapter, hardware implementations of various two dimensional (2D) FFT architectures are described. Hardware and software accelerators for convolutional neural networks, from various research groups are also discussed in this chapter.

# **2.1 FFT Algorithms and Architectures**

Cooley-Tukey is the common algorithm to find DFT of a sequence. DFT can be computed in a faster method using FFT, since it reduces the complexity from  $O(N^2)$  to  $O(Nlog_2N)$  as compared to DFT J.W.Cooley and J.W.Tukey. (1965). One dimensional Discrete Fourier Transform for x(n), an N point sequence, can be computed as Proakis and Manolakis (1996)

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk} \quad k = 0, 1, 2, \dots N - 1$$

(2.1)

where  $W_N$ , the Twiddle Factor, denotes the  $N^{th}$  primitive root of unity, with its exponent evaluated to *modulo* N and is introduced by the Equation (2.2),

$$W_N = e^{-2\pi i/N} \tag{2.2}$$

Each of the coefficients in a DFT requires N complex multiplications and N - 1 complex additions. Hence, for an N-point DFT,  $N^2$  complex multiplications and N(N - 1) complex additions are required. An N-point inverse DFT (IDFT) can be calculated as given in Equation (2.3),

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) W_N^{-nk} \quad n = 0, 1, 2, \dots N - 1$$

(2.3)

IDFT requires few more logic like division and conjugate operation apart from the logic applied in DFT.

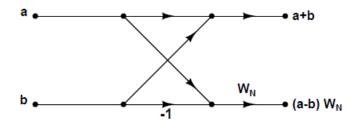

Figure 2.1: Butterfly diagram of Radix-2 DIF FFT

#### 2.1.1 Radix-2 Cooley-Tukey FFT

Most of the applications which uses Cooley-Tukey FFT, has a block-length N, which are powers of two or four. If the block-length  $2^m$  is factorized as  $2 \times 2^{m-1}$ , then it is called radix-2 FFT Blahut (2010). The decomposition size of an FFT is denoted using *radix*. Computation of FFTs can be done either in decimation-in-frequency (DIF) or decimation-in-time (DIT) technique. In DIT technique, the N input sequence is divided into two  $\frac{N}{2}$  sequences, which are even and odd sequences of the input, x(n), and their DFTs are computed as shown in Equation (2.4).

$$X_{1}(k) = \sum_{r=0}^{(N/2)-1} x(2r) W_{N/2}^{rk} \quad k = 0, 1, 2, \dots \frac{N}{2} - 1 \quad r = 0, 1, 2, \dots \frac{N}{2} - 1$$

$$X_{2}(k) = \sum_{r=0}^{(N/2)-1} x(2r+1) W_{N/2}^{rk} \quad k = 0, 1, 2, \dots \frac{N}{2} - 1 \quad (2.4)$$

Here the inputs are in bit-reversed order, while outputs are in natural order. DIT follows in-place computation, where the output values are stored in the same registers where the previous input values were stored. This saves significant memory for computation.

In DIF technique, the output sequence X(K) is divided into odd and even sequences as shown in Equation (2.5). Here the output is bit-reversed and input is in natural order.

$$X(2k) = \sum_{n=0}^{(N/2)-1} [x(n) + x(n + \frac{N}{2})] W_{N/2}^{nk} \quad k = 0, 1, 2, \dots \frac{N}{2} - 1$$

$$X(2k+1) = \sum_{n=0}^{(N/2)-1} [x(n) - x(n + \frac{N}{2})] W_N^{nk} W_{N/2}^{nk} \quad k = 0, 1, 2, \dots \frac{N}{2} - 1 \quad (2.5)$$

Butterfly diagram of radix-2 DIF technique is shown in Fig. 2.1. The computational complexity of both DIT and DIF are same and both follow in-place computation.

Figure 2.2: Radix-4 DIF FFT Butterfly

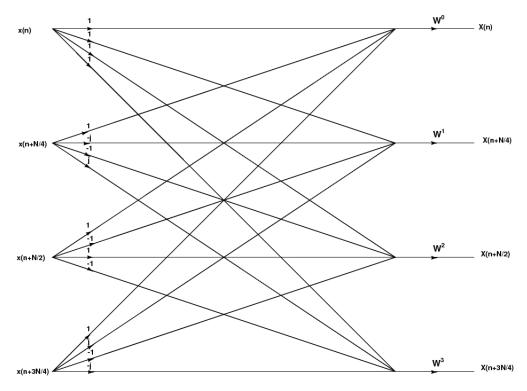

# 2.1.2 Radix-4 FFT

If the block-length  $4^m$  is factorized as  $4 \times 4^{m-1}$ , then it is called radix-4 FFT Blahut (2010). Here an *N*-point sequence is decomposed into four smaller sequences as given in Equation (2.6).

$$X(4k) = \sum_{n=0}^{(N/4)-1} [x(n) + x(n + \frac{N}{4}) + x(n + \frac{N}{2}) + x(n + 3\frac{N}{4})]W_{N/4}^{nk}$$

$$X(4k+1) = \sum_{n=0}^{(N/4)-1} [x(n) - jx(n + \frac{N}{4}) - x(n + \frac{N}{2}) + jx(n + 3\frac{N}{4})]W_N^n W_{N/4}^{nk}$$

$$X(4k+2) = \sum_{n=0}^{(N/4)-1} [x(n) - x(n + \frac{N}{4}) + x(n + \frac{N}{2}) - x(n + 3\frac{N}{4})]W_N^{2n} W_{N/4}^{nk}$$

$$X(4k+3) = \sum_{n=0}^{(N/4)-1} [x(n) + jx(n + \frac{N}{4}) - x(n + \frac{N}{2}) - jx(n + 3\frac{N}{4})]W_N^{3n} W_{N/4}^{nk} (2.6)$$

Radix-4 butterfly diagram is given in Fig. 2.2.

#### 2.1.3 2D FFT

A two dimensional Fourier transform can be computed from one dimensional FFT. An N×N 2D FFT can be computed from 2N one dimensional FFT computations, where N is the sequence length. A two dimensional DFT of size N×N, with inputs  $x(i_1, i_2)$  is given as,

$$y(k_1, k_2) = \sum_{i_1=0}^{N-1} \sum_{i_2=0}^{N-1} x(i_1, i_2) W_N^{k_1 i_1 + k_2 i_2}$$

where  $k_1, k_2 = 0, 1, 2, \dots, N-1$

(2.7)

Using two, one dimensional DFTs, a 2D DFT can be performed based on Row-Column (RC) decomposition algorithm, as given in Equation (2.8).

$$X(k_{1}, i_{2}) = \sum_{i_{1}=0}^{N-1} x(i_{1}, i_{2}) W_{N}^{k_{1}i_{1}}$$

$$where \quad k_{1} = 0, 1, 2, \dots N - 1$$

$$Y(k_{1}, k_{2}) = \sum_{i_{2}=0}^{N-1} X(k_{1}, i_{2}) W_{N}^{k_{2}i_{2}}$$

$$where \quad k_{2} = 0, 1, 2, \dots N - 1$$

$$(2.8)$$

Various FFT algorithms and architectures are available in research papers. FFT architectures and algorithms are chosen based on power, area and throughput requirements Cortes *et al.* (2006) Manolopoulos *et al.* (2007). Different pipelined based and memory based architectures are proposed by several research groups over decades Li (2008)Gold and R.Rabiner (1975)Saponara *et al.* (2012). Pipelined architecture generally gives more area overhead and consumes more power. Pipeline based architectures based on linear decomposition of radix-2 are available in Shousheng He and Torkelson (1998*a,b*); Jeesung Lee *et al.* (2006); Cho and Lee (2013); Oh and Lim (2005); Lin *et al.* (2006). These are either Single-path Delay Feedback (SDF) or Multi-path Delay Commutator (MDC) architectures. In Shousheng He and Torkelson (1996) and Yu-Wei Lin *et al.* (2005) different schemes of SDF and MDC pipelined architectures are discussed. In Yin *et al.* (2016), a two-parallel real FFT based on radix-2 is presented. Their architecture is a pipelined architecture with latency reduction and less hardware complexity. Many more pipelined FFT architectures were proposed in past years Maharatna *et al. et al.*

(2004); Chin-Teng Lin et al. (2006a); Chen et al. (2008); Chih-Peng Fan et al. (2006); Li et al. (2010); Yu et al. (2011); Tang et al. (2010); Reisis and Vlassopoulos (2008); Huggett et al. (2005); Chin-Teng Lin et al. (2006b); Hasan et al. (2003); Cheng and Parhi (2007); Lin and Yu (2007); Yu-Wei Lin et al. (2004); Liao et al. (2018). Radix-2 systolic FFT architecture is presented in Swartzlander (2007). Authors in Garrido et al. (2016) proposes a serial commutator Fast Fourier Transform, with proper data management, to simplify the rotator, and minimize the arithmetic complexity. Memory based designs for 1D FFT are presented in Cohen (1976); Hsiao et al. (2010); Tsai and Lin (2011); Babionitakis et al. (2010b); Ma et al. (2015). Memory based architectures consume more area and less power compared to pipelined FFT, for long size FFTs Xia et al. (2016). Several memory access schemes for 1D FFT are proposed in Xing *et al.* (2017); Huang and Chen (2016); Xia et al. (2016). In Shih et al. (2018), a reconfigurable FFT architecture is proposed, which supports 46 different modes for LTE applications. Various reconfigurable FFTs are also proposed in research papers. FFT of size upto 256 K using radix-4<sup>3</sup> algorithm is presented in Babionitakis *et al.* (2010*b*). Yang et al. propose a multiple stream MDC architecture which computes 128 - 2 K point FFT and achieve memory reduction by an efficient memory scheduling mechanism Yang et al. (2013a). FFT processor to compute 16 - 1 K point FFTs with reconfigurable address generation block is presented in Yutian Zhao et al. (2005). A variable length FFT processor ranging from 512-8 K points, using mixed radix SDF architecture is presented in S.-S. Wang and C.-S. Li (2008). Multi-processor ring based FFT architecture in Guichang Zhong et al. (2006) and CORDIC based cached memory architecture in J.-C. Kuo et al. (2003), have the disadvantage of taking higher number of clock cycles per FFT computation, resulting in higher execution time and lower throughput. FFT processor in Tang et al. (2012) is based on Multi-path Delay Feed-back architecture and supports FFT sizes from 64 - 1 K point. Although these architectures support reconfigurability, they are not scalable in terms of FFT sizes.

Different architectures for 2D FFT has been proposed by various research groups. Software solutions like FFTW Frigo and Johnson (1998), Spiral Puschel *et al.* (2005), gives high performance, but consume more power and are not suitable for embedded system applications. Various hardware solutions such as FFT processor ASICs and FPGA implementations are available in D'Alberto *et al.* (2007), T. (2001), Lenart *et al.*

(2008), Kim *et al.* (2009). A new two dimensional decomposition algorithm is implemented in Yu *et al.* (2011). Here the data is divided into several sub blocks and butterfly operation is performed between these sub blocks. 2D FFT of each of these sub block is computed, where the size of sub block is determined using available FPGA resources. In Chen and Prasanna (2014), several energy optimization techniques are used to develop an efficient and high throughput 2D FFT architecture on FPGA. In Lenart *et al.* (2008) 2D FFT for digital holographic imaging is presented. They have used mixed radices, ie., radix-2 and radix- $2^2$  butterfly units in the 1D FFT. A transpose unit is required after the first 1D FFT block, to compute 2D FFT.

In Akin *et al.* (2012) the issue of off-chip memory bandwidth is addressed. An ILUT based 1D FFT is used to develop a 2D FFT on FPGA in Kee *et al.* (2009). In Akin *et al.* (2012) and Kee *et al.* (2009),  $N^2$  intermediate memory is required after the first phase of FFT. But for the architecture proposed in this thesis, the intermediate memory requirement after performing a 1D FFT reduces to N. Moreover, within a 1D FFT block, there is significant reduction in intermediate RAM.

Output reordering is a major functional block when designing FFT architecture. The purpose of reordering is to convert the non-natural FFT output to natural order. Extensive research papers are available for design and implementation of FFT architecture. But only few papers discuss about output reordering techniques in FFT and its complexity. In OFDM based applications, output reordering is taken care by the preceding block. Hence most of the research papers of FFT focus on design of FFT core alone, rather than bit reversal. An output reordering logic is presented in Chidambaram (2005). But the logic block becomes complex with large sizes of N. In memory based designs, efficient schemes for conflict free addressing is a challenging task Babionitakis et al. (2010b). Address schemes used in memory based FFT architecture will produce the output in reordered form Sorokin and Takala (2011); Hsiang-Sheng Hu et al. (2009). For SDF and MDC architectures, buffers are required at the output, for data reordering. Output reordering in parallel pipelined FFT architectures are highly complex and are discussed in Garrido et al. (2011); Yang et al. (2013b). In F. Kristensen (2003), two buffers each of size N are required to store even and odd FFT outputs for reordering. In Chakraborty and Chakrabarti (2008) single memory of size N is used for bit reversal of even and odd outputs alternatively. In MDF (Multi path Delay Feedback) pipelined architectures  $3 \times N$  memory will be used for output reordering. ie.,  $2 \times N$  will be required in output side and N will be used within the processing elements Huang and Chen (2012). In Garrido *et al.* (2011) a framework for performing bit reversal in output data is proposed. They use minimum number of registers for calculating bit reversal and new circuits were designed for output reordering in different radices. An algorithm for performing bit reversal is discussed in Marti-Puig and Reig Bolano (2009). But the algorithm is applicable only if transform length is a power of four. In most of these architectures, either a dedicated hardware or significant memory is required for reordering. Our architecture does not require buffers for output reordering. This is possible using the six-bit control signal used in our FFT.

# 2.2 Convolutional Neural Networks

Neuromorphic computing, which is based on brain-inspired computing has become a contrast architecture to von Neumann architecture. Neuromorphic architectures are highly appreciated for their parallel and fast processing capabilities, and also for their low power requirement in the context of Dennard scaling Esmaeilzadeh *et al.* (2011), as Moore's law is about to end and Dennard scaling demands for more power. Neuromorphic architecture are suitable candidates for implementation of machine learning algorithms. Researchers work on developing new network models that mimic biological brain, along-with developing new machine learning algorithms. Machine learning is a sub-field of artificial intelligence, where the computers have learning abilities without being programmed explicitly.

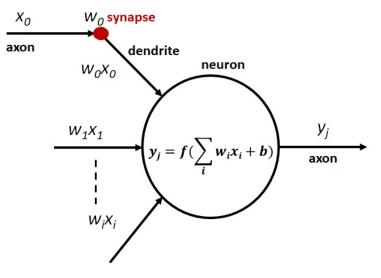

In brain-inspired computing, an algorithm will take some of the functionalities in a way, in which the brain functions. Computations in brain are centered on *neurons*. There are billions of neurons in human brain, which are interconnected each other. Each of the neuron is a processing unit, which receives many real inputs and produces a single real output. The inputs enter a neuron through *dendrites* and leaves through *axons* as shown in Fig.2.3. These input-output signals are named as *activations*. Axon is connected to the dendrite through a *synapse*. As seen from Fig. 2.3, the input signal  $x_i$  is scaled by the *weight*  $w_i$ , when it is passed through the synapse. Learning factor of the brain is indicated as the *weight*, and various outputs are generated depending

Figure 2.3: Neuron in the brain

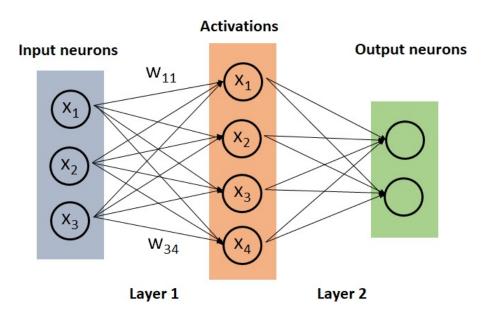

Figure 2.4: Typical Neural Network

on the variations in these weights. In general, neural networks involves computation of a neuron as the weighted sum of all the input values. This is given in Equation (2.9) where *b* denotes *bias*,

$$Y_j = f(\sum_i w_i x_i + b) \tag{2.9}$$

Fig. 2.4 shows a simple neural network, with three input neurons receiving three different values and propagating it to the middle layer, which is called *hidden layer*. The weighted sums from many hidden layers are given to output neurons, which are the outputs of a neural network. If the neural network has more than one hidden layer, then it is generally referred to as *deep neural network* and the area in which they are used is

#### deep learning.

Recent breakthrough in the advancement of deep learning has led to deployment of Deep Neural Networks (DNNs) for most of the artificial intelligent tasks. DNNs have become a dominant approach for a variety of machine learning tasks like object detection, image classification and recognition, autonomous automobiles, autonomous speech processing and so on. DNNs are inspired by the functionality and behavior of human brain, where the computations are performed by 'neurons'. *Training* of a network refers to a process where an algorithm will learn to approach a problem. Training involves selection of *weights* of the network so as to produce the desired output. Running a network with these computed weights is called as *inference*. In other words, inference is referred as execution of the feed forward path of a neural network. Training can be performed using *supervised learning* (with labeled classes), *unsupervised learning* (without labeled classes), *semi-supervised learning* (a subset being labeled) or *reinforcement learning* (where the state of environment is known, to maximize the output) techniques. Another technique used is *transfer learning* for better precision, where the network is learned from previously adjusted weights.

Typically, Artificial Neural Networks (ANN) are composed of Multi-Layer Perceptrons (MLP), which are fully connected layers, where all output neurons connected to all input neurons. Here, the weights (coefficients) to be stored is significantly high and the computation is also increased. One way to reduce the huge memory requirement is to set some of the weights to zero, thereby removing some connections, without losing the precision. Another way to reduce the memory requirement is *weight sharing*. Here same set of weights can be used to calculate the output. An efficient technique for reducing the memory and computation is to use convolutions as computation instead of fully connected layers. Here weight sharing and windowing techniques are used for reducing the complexity.

Convolutional neural networks (CNNs), a variant of DNN, is a promising solution to wide range of applications like robotics, weather forecasting, video surveillance and applications in the field of medicine like cancer detection etc. CNNs out-perform human intelligence in many image classification tasks. CNNs are composed of different layers namely, convolutional layer (referred as CONV), pooling layer (POOL), normalization, ReLU (recti-linear unit) and fully connected (referred as FC) layers. Convolution layer

extracts various features of the input image, while sub-sampling is done by POOL layers. It is followed by FC layers which performs classification of the feature map. CONV layer convolves the input feature map with filter and produces output feature map. Filter weights are calculated during the training process. Pooling layer is done either with MAX or AVERAGE operation. Each neuron in an FC layer is connected to all other neurons in the previous layer, which increases the number of weights in FC layer and makes it a memory intensive layer. But in CONV layer, computations are higher and filter coefficient storage requirement is less compared to FC layer.

Non-linearity is introduced after CONV layers or FC layers using activation functions. Sigmoid and Hyperbolic tangent functions were considered as traditional activation functions, whereas Rectified Linear Unit (ReLU), Leaky ReLU, Exponential ReLU were referred as modern activation functions. Pooling combines a set of values into a smaller set of values. Pooling is done on non-overlapping blocks of values. A stride greater than one is used to minimize the dimension of feature map. In Max pooling, maximum value in the block is selected where as in Average pooling, average value of the block is taken into account. Batch normalization is performed at the layer input activations so as to have zero mean and standard deviation as unity. This normalized value is then scaled and shifted. Drop out is also a regularizer, which is used in many CNN models. Sometimes batch normalization allows drop outs to be omitted because of the presence of noise in statistical estimations in the variables. Performance increases when the model is regularized well using drop out.

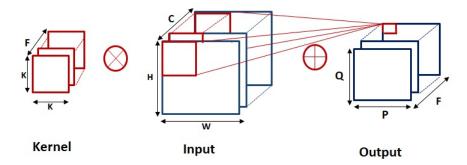

Convolutions in CNN are 2D operations, where filter weights are multiplied with each element in the feature map and are summed together. ie., it involves multiply and accumulate (MAC) operations of filter weights and input feature map. Each element in the input feature and filter is multiplied and accumulated to get the corresponding element in the output feature map. Consider M channels of  $K \times K$  filter, and a total of N such filters. Also consider M channels of  $H \times W$  input feature maps, for performing convolution. Each filter performs convolution on the input feature map with a stride of S, and generates the output feature map, Y. Element (u, v) in  $n^{th}$  filter,  $m^{th}$  channel is represented as  $G_{n,m,u,v}$  and input element (x, y) in  $m^{th}$  channel is denoted as  $D_{i,m,x,y}$ .

Figure 2.5: Convolution Operation

Convolution is given by the formula as in (2.10),

$$Y_{i,n,x,y} = \sum_{m=1}^{M} \sum_{u=1}^{K} \sum_{v=1}^{K} D_{i,m,x+u+S,y+v+S} \times G_{n,m,u,v}$$

(2.10)

Entire output of convolving the image with filter can be written as in (2.11),

$$Y_{i,n} = \sum_{m=1}^{M} D_{i,m} * G_{n,m}$$

(2.11)

where \* denotes correlation.

Convolution operation is shown in Fig. 2.5.

Various convolution architectures were proposed by different research groups over the last few years. GPU based 2D convolver proposed in Iandola *et al.* (2013) reduces memory communication by reorganizing the convolution algorithm and working on few threads. In Ciobanu and Gaydadjiev (2013), a vectorized separable 2D convolver optimized for polymorphic register files, for high performance, is proposed and implemented in GPU. GPU implementations give high performance but they are not suitable for embedded applications due to their high power consumption. Various FPGA based convolvers are presented in Perri *et al.* (2005); Aguilar-González *et al.* (2019); Rao *et al.* (2016); Chang and Sha (2017); Russo *et al.* (2012); StrÃűm (2016); Mohammad and Agaian (2009). In Perri *et al.* (2005) a reconfigurable architecture for 2D convolution is presented, which uses 8-bit and 16-bit fixed point arithmetic. Here even though high performance is achieved, precision is degraded. CAPH language has been used in the convolver design in Aguilar-González *et al.* (2019), to reduce the design time. The design flow is a data-flow model, where tokens are interchanged through a network. Here also 16-bits are taken for representation. Reconfigurable one dimensional convolution architecture presented in Rao *et al.* (2016) has been implemented in both ASIC and FPGA. They have used separable convolutions for implementation.

2D convolution for CNN presented in Chang and Sha (2017), uses singular value decomposition approximation method, which in turn transformed to conventional row and column technique. Russo *et al.* (2012) compare GPU and FPGA implementations, which concludes that GPU achieves high performance with high power consumption, whereas FPGA can operate in small boards with less power consumption. Convolution architecture for CNN proposed by Wang *et al.* (2016) uses parallel finite impulse response algorithm for convolution and implemented in 90nm CMOS process. StrÃűm (2016) presents an architecture with 16 parallel convolutions and implemented in FPGA. Mohammad and Agaian (2009) also uses fixed point arithmetic with less precision for implementation. The above mentioned papers follow conventional technique for computation of convolutions. This uses more hardware resources as the number of multiply and accumulate (MAC) operations are very high in conventional technique.

Several GPU accelerators for Convolutional Neural Networks are available in various research papers. In Li *et al.* (2016), performance evaluation of CNN on Tesla K40c, for various kind of implementations is presented. Training period of AlexNet models are evaluated for various frameworks using GPU in Kim *et al.* (2017). FFT based CNN implementations using Torch 7 environment were performed on GeForce GTX Titan GPU in Mathieu *et al.* (2013). GPU accelerators for CNN are also presented in Chakradhar *et al.* (2010); Krizhevsky *et al.* (2012); Szegedy *et al.* (2015); Gupta *et al.* (2015). Many open-source frameworks for deep learning like Caffe Jia *et al.* (2014), Torch Collobert *et al.* (2011) Theano Bergstra *et al.* (2010) etc. were also introduced which can use CUDA programming. Specific libraries like cuDNN Chetlur *et al.* (2014) are also available for accelerating CNNs.

ASIC based implementations of CNN are presented in Tu *et al.* (2017); Chen *et al.* (2014, 2016). Authors in Chen *et al.* (2014) propose an architecture with interconnected nodes which contains 64 nodes. ASIC based accelerator proposed by Chen *et al.* (2014), gives high performance but with limitations in flexibility. A reconfigurable and scalable CNN architecture is presented in Tu *et al.* (2017) with reconfigurable deep neural architecture (DNA). Fast FIR Algorithm (FFA) has been introduced in Wang *et al.* (2018*a*) to develop a reconfigurable convolution core, with high power efficiency.

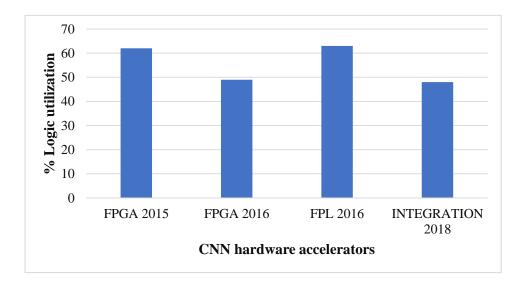

Figure 2.6: Hardware Utilization for AlexNet implementation